# A ROM-LESS DIRECT DIGITAL FREQUENCY SYNTHESIZER BY USING TRIGONOMETRIC QUADRUPLE ANGLE FORMULA §

Chua-Chin Wang †, Hsien-Chih She, and Ron Hu ‡

Department of Electrical Engineering National Sun Yat-Sen University Kaohsiung, Taiwan 80424 email: ccwang@ee.nsysu.edu.tw

#### ABSTRACT

A ROM-less direct digital frequency synthesizer (DDFS) employing trigonometric quadruple angle formula is presented. The spectral purity is better than -130 dBc worst case spur. The resolution is up to 13 bits. Neither any scaling table nor error correction tables are required. The maximum error is mathematically analyzed. The word length of each multiplier is carefully selected in the digital implementation such that the error range is limited and the resolution is preserved.

#### 1. INTRODUCTION

Ever since the low-cost RF CMOS technology becomes the challenger of its conventional discrete counterpart, the spectral quality of the frequency synthesizers in a single chip solution has been demanded to possess better purity. Direct digital frequency synthesizers (DDFSs) are very much preferred in some modern communication systems owing to their advantages over PLL-based solutions, e.g., fast settling time, sub-Hertz frequency resolution, continuous-phase frequency switching and low phase noise [4]. The bottleneck of the DDFS method is the generation of a pure sinusoidal output. Many prior works were proposed to resolved this problem, including ROM-based lookup tables [1], [2], [3], [4], [5], or scaling and error correction tables [6]. All of the ROM-based solutions suffer from ROM's intrinsic drawbacks which are slow speed, large area, and high power consumption. Sodagar et al. proposed a ROM-less DDFS by using 2nd-order parabolic approximation [6]. However, in order to reduce the conversion error, a scaling table and an error correction table (or generator) are needed. It, thus, not only deteriorates the speed performance, but also affect the resolution of the output word length. In this paper, we propose a novel ROM-less design for DDFSs, which utilizes trigonometric  $4\theta$  formula to attain the smaller error range.

## 2. $4\theta$ ANGLE APPROXIMATION

A basic idea to carry out the ROM-less DDFS is to utilize the trigonometric quadruple angle formula such that the irregularity of the scaling and error correction difficulties in [6] will be eliminated. In addition, the upper bound of the error range can be analytically solved.

## 2.1. Trigonometric 1st-order $4\theta$ approximation

The double angle equality is well known as

$$\cos 2\theta = 2\cos^2\theta - 1 = 1 - 2\sin^2\theta \tag{1}$$

The Eqn.(1) can be re-arranged as the following equality if  $\theta$  is replaced with  $2\theta$ .

$$\cos 4\theta = 2\cos^2 2\theta - 1 \tag{2}$$

$$= 1 - 8\sin^2\theta(1 - \sin^2\theta) \tag{3}$$

Since the range of  $4\theta$  is limited in  $[0, \frac{\pi}{2}]$  [4], the range of  $\theta$  is  $[0, \frac{\pi}{8}]$ . Thus,  $\sin \theta \approx \theta$ . Eqn.(3) becomes

$$\cos 4\theta \approx 1 - 8\theta^2 (1 - \theta^2), \quad 0 \le \theta \le \frac{\pi}{8}$$

(4)

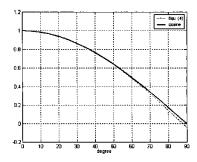

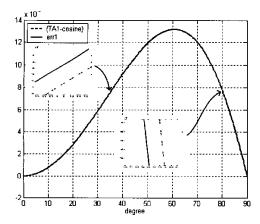

Fig. 1 shows the comparison of true cosine function and Eqn.(4). Notably, the maximum amount of error occurs at  $90^{\circ}$ . In order to minimize the amount of error, the upper bound must be chosen to be smaller than  $\frac{\pi}{8}\approx 0.3927$ . This bound should also be easily converted into a digital representation which will make the physical implementation feasible. The simulink of MATLAB is employed to find such a proper bound which will meets the requirement of at least 12-bit output resolution. The simulation results suggest a nice selection at  $\frac{3135}{8192}$  with an error  $\leq 2.4 \times 10^{-4}$ . Hence, we re-define our 1st-order approximation method, called TA1(x) (1st-order trigonometric approximation), as follows.

$$TA1(x) = 1 - 8x^2(1 - x^2), \quad 0 \le x \le \frac{3135}{8192}$$

(5)

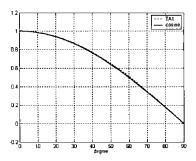

Fig. 2 illustrates the actual cosine function and TA1(x), while the difference of these two functions,

$<sup>\</sup>$  This research was partially supported by National Science Council under grant NSC 89-2215-E-110-014.

<sup>†</sup>Prof. Wang is the contact author.

<sup>‡</sup>Dr. Hu is Ğeneral Manager of Asuka Microelectronics Inc., Hsin-Chu, Taiwan.

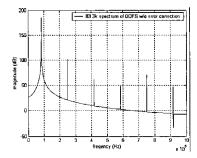

imum error attained graphically is  $13 \times 10^{-3}$  which is smaller than  $15.625 \times 10^{-3} = \frac{1}{2^6}$ . It indicates that the 1st-order approximation has at least 6-bit resolution. Fig. 4 produced by MATLAB simulation shows that the worst case spurious is -84 dBc by using the TA1 approximation, which is no error correction at all.

Since the error function,  $\operatorname{err}(x) = \operatorname{TA1}(x) - \cos \theta$ , is not a good function to be implemented digitally. We propose to use a polynomial function to fit the error function. The steps are summarized as follows.

- Keep dividing TA1(x)(1 TA1(x)) by 2 until the maximum of TA1(x)(1 - TA1(x)) is close to the maximum of err(x).

- 2). A scaling factor, K, is chosen to further reduce the error between  $\mathrm{TA1}(x)(1-\mathrm{TA1}(x))$  and  $\mathrm{err}(x)$ . The K must be digitally representable. Besides, the final error must be less than  $\frac{1}{2^{12}}=2.4\times10^{-4}$  to ensure the resolution.

The optimization procedure is carried out by simulink of MATLAB. The final optimized error function becomes as follows.

err1(x) =

$$K \cdot (0.5)^4 \text{TA1}(x) \cdot (1 - \text{TA1}(x))$$

, (6)

$\approx \text{TA1}(x) - \cos \theta$ ,

where  $K = (0.84375)_{10} = (0.11011)_2, 0 \le \theta \le \frac{\pi}{2}$ , and  $0 \le x \le \frac{3135}{8192}$ . Fig. 5 illustrates the tuned err1(x) is very close to the err(x) function, which is TA1(x) –  $\cos \theta$ .

## 2.2. 2nd-order approximation

A simple thought to further reduce the amount of error between the cosine function and the approximation equation is to utilize a 2nd-order difference method, which is given as follows.

$$TA2(x) = TA1(x) - err1(x), \quad 0 \le x \le \frac{3135}{8192},$$

(7)

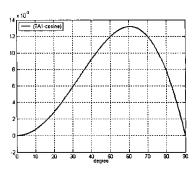

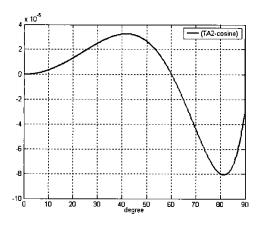

Fig. 6 shows (TA2 - cosine) graphically. We attain the maximal amount of error from the figure is  $0.8 \times 10^{-4} < 1.22 \times 10^{-4} = \frac{1}{2^{13}}$ , we conclude that the output resolution of our proposed method is guaranteed to be 13 bits, which is more accurate any prior work. In other words, a trigonometric  $4\theta$  approximation with error correction for sinusoidal output is attained.

## 2.3. Analytic solutions

It is also an interesting thing to find out where the maximal error is. We represent the difference between TA2 and cosine as another error function.

$$err2(x) = TA2(x) - \cos \theta$$

where

$$0 \le x \le \frac{1}{8192}$$

,  $0 \le \theta \le \frac{1}{2}$  (8)

$TA2(x) = TA1(x) - A \cdot TA1(x)(1 - TA1(x))$ ,

where  $A = 0.84375 \cdot (0.5)^4$  (9)

$$TA1(x) = 1 - 8x^2(1 - x^2)$$

(10)

By substituting Eqns.(9) and (10) into Eqn.(8), we obtain the entire err2(x). Then, we take the first order derivative of err2(x) and solve the solution given that err2'(x) = 0 to attain the following equations.

err2'(x) = TA2'(x) - (cos

$$\theta$$

)' = 0,

0 = (32x^3 - 16x)(16Ax^4 - 16Ax^2 + A + 1)

-(cos  $\theta$ )'

0 = (32x^3 - 16x)(16Ax^4 - 16Ax^2 + A + 1)

+  $\frac{8192\pi}{6270}$  sin  $\theta$ , where  $\theta = \frac{8192\pi}{6270}x$  (11)

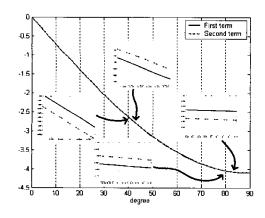

By graphically solving the two terms in Eqn.(11) as shown in Fig. 7, there are two intersections between the two curves in which the solid line denotes the first term, while the dash line is the second term. The locations of the two intersections exactly match the maximum and minimum of the curve in Fig. 6, respectively. This phenomenon verifies that our method indeed provide a high resolution result.

## 2.4. Digital system implementation

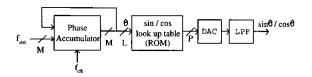

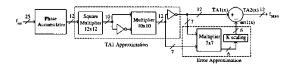

Fig. 8 is a typical implementation of DDFSs in prior works. The slow and large ROM not only occupies a significant portion of the chip (or board) area, it also degrades the speed. We propose our digital implementation basing upon the proposed  $4\theta$  approximation method in Fig. 9.

## 3. SYSTEM-LEVEL SIMULATION

Modelsim of Mentor and MATLAB of Mathworks are the S/W tools to proceed the system-level simulations. The steps that we adopted are summarizes as follows.

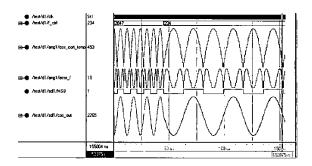

- (1). The design in Fig. 9 is coded by Verilog which is then simulated by Modelsim. The decimal output data in a 12-bit format are collected. Fig. 10 shows the result of this part of work.

- (2). The collected data are fed into MATLAB. The FFT command is executed to attain the spectrum.

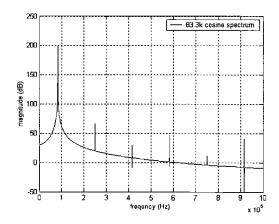

Fig. 11 illustrates the spurious performance of the proposed method is as high as -130 dBc, which is far better than any prior works. Table 1 summarizes the performance of our work and prior methods.

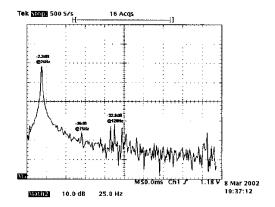

We, then, implement the proposed design by Altera APEX20KE FPGA board and Analog Device's AD1854 DAC. This DAC is for audio application and the input is serial. The performance is measured by Tecktronix TDS 680B oscilloscope. Fig. 12 shows the measured sprectum of the proposed synthesizer.

|       | resolution | spurious   |

|-------|------------|------------|

| [1]   | 10 bits    | -55 dBc    |

| [4]   | 11 bits    | -55 dBc    |

| [5]   | 12 bits    | -98.75 dBc |

| [6]*  | 10 bits    | -62.8 dBc  |

| ours* | 12 bits¶   | -130 dBc   |

Table 1: Performance comparison (\*: ROM-less method, ¶: Since there is no 13-bit DAC, we use 12-bit resolution in our simulation.)

## 4. CONCLUSION

In this paper, we have presented a novel method utilizing the quadruple angle equality equation to reduce the spurious of the DDFSs. The 2nd-order error correction has been simulated to justify the capability of subside the noise power of the harmonics.

#### 5. REFERENCES

- G. Van Andrews, et al., "Recent progress in wideband monolithic direct digital synthesizers," IEEE MTT-S Inter. Microwave Symp. Digest, vol. 3, pp. 1347-1350, 1996.

- [2] M. J. Flanagan, and G. A. Zimmerman, "Spurreduced digital sinusoid synthesis," *IEEE Trans. on Comm.*, vol. 43, no. 7, pp. 2254-2262, July 1995.

- [3] V. F. Kroupa, V. Cizek, J. Stursa, and H. Svandova, "Spurious signals in direct digital frequency synthesizers due to the phase truncation," *IEEE Trans. on Ultrasonics, Ferroelectrics, and Frequency Control*, vol. 47, no. 5, pp. 1166-1172, Sep. 2000.

- [4] G. W. Kent, and N.-H. Sheng, "A high purity, high speed direct digital synthesizer," 1995 49th IEEE Inter. Frequency Control Symp., pp. 207-211, 1995.

- [5] R. Larson, and S.-L. Lu, "Interpolation-based digital quadrature frequency," 13th Annual IEEE Inter. ASIC/SOC Conf., pp. 48-52, 2000.

- [6] A. M. Sodagar, and G. R. Lahihi, "A novel architecture for ROM-less sine-output direct digital frequency synthesizers by using the 2nd-order parabolic approximation," 2000 IEEE/EIA Inter. Frequency Control Symp. and Exhibition, pp. 284-289, 2000.

Figure 1: comparison of cosine and Eqn.(4)

Figure 2: comparison of cosine and TA1(x)

Figure 3: err1(x)

Figure 4: spurious spectrum of TA1(x)

Figure 5: optimized err1(x)

Figure 6: TA2(x)

Figure 7: graphical solutions for maximum error in err2

Figure 8: the architecture of prior ROM-based DDFSs

Figure 9: our proposed ROM-less DDFS

Figure 10: Verilog simulation results

Figure 11: spurious performance of the proposed  $$\operatorname{DDFS}$$

Figure 12: measured spectrum of the proposed DDFS