ELSEVIER

Contents lists available at ScienceDirect

## Microelectronics Journal

journal homepage: www.elsevier.com/locate/mejo

# Wide-range CTAT and PTAT sensors with second-order calibration for on-chip thermal monitoring

Chua-Chin Wang\*, Wen-Je Lu, Tzu-Chao Wu

National Sun Yat-Sen University, Department of Electrical Engineering, 70 Lian-Hai Road, Kaohsiung, Taiwan

#### ARTICLE INFO

Article history:

Received 7 September 2014

Received in revised form

22 May 2015

Accepted 5 June 2015

Available online 14 July 2015

Keywords:

Second-order effects

PTAT sensor

CTAT sensor

Temperature sensor

Low-cost

Second-order calibration

#### ABSTRACT

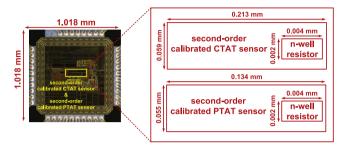

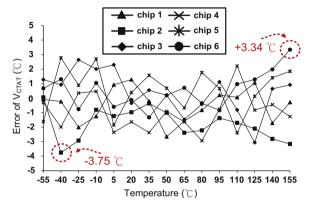

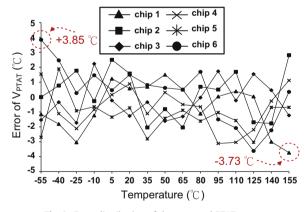

This paper presents wide-range complementary to absolute temperature (CTAT) and proportional to absolute temperature (PTAT) sensors with second-order calibration for on-chip thermal monitoring. Particularly, a current mirror and an n-well resistor are used in these sensors to eliminate the second-order term of the temperature coefficient to linearize the transfer function between the output voltage and the temperature. The proposed CTAT and PTAT sensors are implemented on silicon using a typical 0.18  $\mu$ m CMOS process. The core area of the CTAT and PTAT sensors is 0.0125 mm² and 0.0074 mm², respectively. In the range from -55 °C to 155 °C, the worst deviation of the CTAT and PTAT temperature sensors is measured to be -3.75 °C to +3.34 °C and -3.73 °C to +3.85 °C, respectively. The maximum non-linearity reduction of the CTAT and PTAT sensors is 59.84% and 87.48%, respectively, by the proposed second-order calibration. Notably, the overhead area of the CTAT and PTAT sensors is only 0.64% and 1.08%, respectively.

© 2015 Elsevier Ltd. All rights reserved.

### 1. Introduction

It is well known that more transistors have been integrated in a chip by using advanced CMOS technologies. When many transistors are integrated and realized on a single die, the power density as well as the temperature will rise inevitably. Moreover, the chip with high switching activities will generate massive heat (namely hot spot) [1]. Another critical issue is the range of the temperature. The harshest temperature range is demanded by electrical vehicles (EV) and military equipments, which are  $-40\,^{\circ}\text{C}$  to  $125\,^{\circ}\text{C}$  and  $-55\,^{\circ}\text{C}$  to  $125\,^{\circ}\text{C}$ , respectively [2–4]. Temperature sensors are then required to monitor the temperature of those chips in these applications in such a wide temperature range to ensure that no hazards would be caused by over heat problems.

Many prior temperature sensors relied on threshold voltage detection to estimate the temperature [5–8]. The accuracy in a very wide range is still a challenge regarding on-chip temperature sensing. Vaz et al. proposed a temperature sensor for human body temperature monitoring, where a large resistor is used to cancel temperature non-linearity components of the saturation current [7]. However, this design was meant for low temperature range. Several logic-based design temperature sensors have also been proposed [1,9]. Chung and Yang proposed an all-digital temperature sensor, where serious

process and non-linear effects still exist [1]. The reason is that the process variation and second-order effects of MOSs in all digital circuits are hard to be detected and then calibrated. A few timedomain temperature sensors were also reported [10-13]. Chen et al. proposed a time-domain temperature sensor based on a successive approximation algorithm [10]. The successive approximation algorithm, however, costs a large area overhead. Meanwhile, the high linearity and second-order effects calibration methods were reported [14-18]. Lin et al. proposed a non-linear calibration method by isolating body effect. This design, however, did not consider the process variation [14]. Jeong and Ayazi disclosed a process offset cancellation method by applying an identical circuit to realize temperature sensors [17]. The reported process compensation and second-order effects calibrated methods usually need a large area to realize compensation and calibration circuits [10-18]. Many low-cost calibration methods were also proposed [19-21]. Fisk and Hasan showed a method using the correlation between pinch-based resistance and substrate bipolar temperature gradient to carry out processcompensation [20]. Besides, Souri et al. also proposed high accuracy and low-power temperature sensors [22,23], where silicon on insulator (SOI) process was used to attain a much wider temperature range and low power consumption [22]. Another prior design used dynamic threshold MOSTs (DTMOSTs) and an inverter-based secondorder zoom analog-to-digital converter (ADC) to achieve high accuracy and low power [23]. However, the SOI process, DTMOSTs, and the other prior calibration technologies must pay high die area and cost [14-26].

<sup>\*</sup> Corresponding author. Tel.: +886 7 5252000x4144; fax: +886 7 5254199.

E-mail addresses: ccwang@ee.nsysu.edu.tw (C.-C. Wang),

wen@vlsi.ee.nsysu.edu.tw (W.-J. Lu), wuachao@vlsi.ee.nsysu.edu.tw (T.-C. Wu).

In this study, we propose complementary to absolute temperature (CTAT) and proportional to absolute temperature (PTAT) sensors with low-cost second-order calibration to resolve all the mentioned problems. By using the proposed second-order calibrated CTAT and PTAT sensors consisting of a current mirror and an n-well resistor, the linearity can be enhanced.

## 2. Wide-range temperature sensor

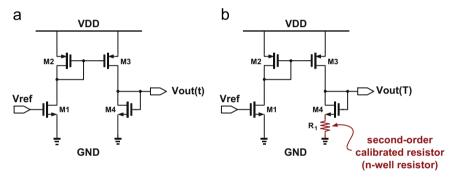

Fig. 1(a) shows the schematic of the non-calibrated temperature sensor composed of 2 PMOSs and 2 NMOSs [15]. The non-calibrated temperature sensor will attain a positive or negative T-to-V (temperature-to-voltage) transfer curve by adjusting length and width of MOSs. Since this method is based on threshold voltage detection, the linearity of temperature sensors is affected by threshold voltage and mobility variations. Particularly, a significant second-order effect has been well known to exist between the saturation current of MOSs and the temperature. A simple thought is that the linearity of the transfer curve can be more linearized if this second-order effect is reduced or even cancelled. Therefore, we propose a second-order calibrated

temperature sensor, which utilizes an n-well resistor to calibrate the second-order effect.

## 2.1. Theory of second-order temperature calibration

Fig. 1(b) shows the second-order calibrated temperature sensor, which is composed of 2 PMOSs, 2 NMOSs, and an n-well resistor. The output voltage of the proposed temperature sensor is expressed as

$$Vout(T) = V_{GS4}(T) + I_{sat}(T)R(T)$$

(1)

where T is the absolute temperature in degrees of Kelvin,  $V_{\rm CS4}(T)$  is the voltage difference between gate and source voltage of M4 with

**Table 1**Simulations of n-well resistor characteristic.

|                                                                                               | $R_0$                         | γ                                                                                           | γ'                                                                                          |

|-----------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| R(T) <sub>5 K</sub><br>R(T) <sub>25 K</sub><br>R(T) <sub>125 K</sub><br>R(T) <sub>625 K</sub> | 5 K<br>25 K<br>125 K<br>625 K | $2.905 \times 10^{-3}$ $2.905 \times 10^{-3}$ $2.906 \times 10^{-3}$ $2.911 \times 10^{-3}$ | $1.321 \times 10^{-5}$ $1.421 \times 10^{-5}$ $1.327 \times 10^{-5}$ $1.320 \times 10^{-5}$ |

Fig. 1. Schematics of (a) non-calibrated temperature sensor, and (b) second-order effects calibrated temperature sensor.

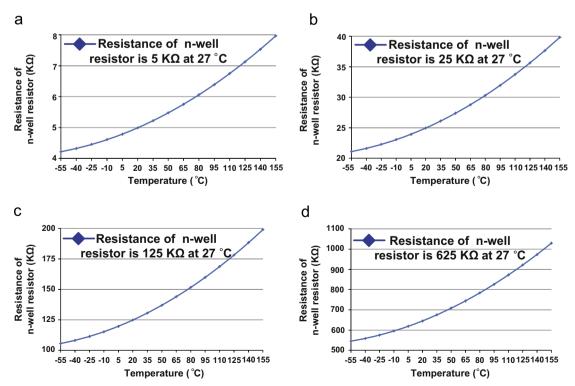

Fig. 2. Simulations of an n-well resistor characteristic curve (a) resistance=5 K Ω, (b) resistance=25 K Ω, (c) resistance=125 K Ω, and (d) resistance=625 K Ω.

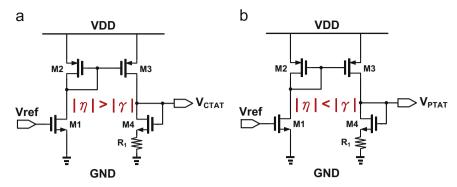

Fig. 3. Schematics of (a) second-order calibrated CTAT sensor, and (b) second-order effects calibrated PTAT sensor.

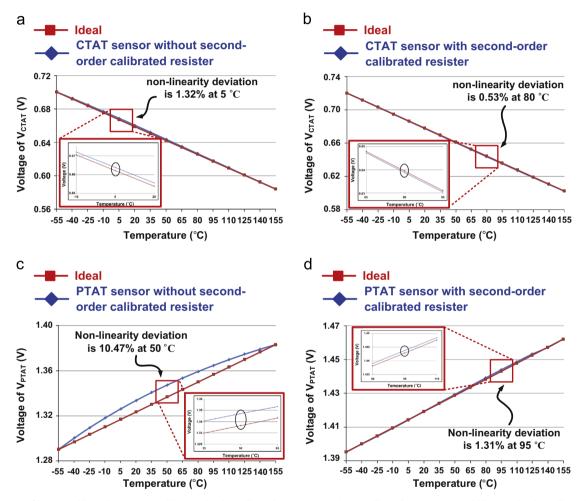

Fig. 4. Simulations of (a) non-calibrated CTAT sensor, (b) second-order calibrated CTAT sensor, (c) non-calibrated PTAT sensor, and (d) second-order calibrated PTAT sensor.

temperature variation,  $I_{\text{sat}}(T)$  is the saturation current in M4, R(T) is the resistance of the n-well resistor.  $I_{\text{sat}}(T)$  is expressed as follows [6].

$$I_{\text{sat}}(T) = \frac{1}{2}u(T)C_{\text{ox}}\frac{W}{L}[V_{\text{GS4}}(T) - V\text{th}(T)]^2$$

(2)

where W is the channel width of M4, L is the channel length,  $C_{ox}$  is the oxide capacitance, u(T) is the mobility, and Vth(T) is the threshold voltage. u(T) and Vth(T) are defined as follows [6]:

$$u(T) = u_0 \left(\frac{T}{T_0}\right)^{\text{UTE}} \tag{3}$$

$$Vth(T) = Vth0 - \alpha(T - T_0)$$

(4)

where  $\alpha$  can be written as  $\frac{1}{T_0}$ (KT1+ $\frac{\text{KT1L}}{\text{Left}}$ +KT2 ×  $V_{\text{BS}}$ ),  $T_0$  is roughly equal to 298°K or 25°C, UTE is a negative temperature coefficient of the mobility, Vth0 is the threshold voltage at  $T_0$ ,  $u_0$  is the mobility at  $T_0$ , KT1 is the temperature coefficient of the threshold voltage, KT1L is the temperature coefficient of channel length, KT2 is a body-bias coefficient of the threshold voltage with temperature variation,  $V_{\text{BS}}$  is the voltage difference between bulk and source voltage of M4. Notably, UTE is between -1.2 and -2.0, and  $\alpha$  is in the range of 0.5-3.0 mV/°C [10]. According to the above equations and the current mirror characteristic, when all MOSs are saturated,  $I_{\text{D1}}$  and  $I_{\text{D4}}$

**Table 2**Calibration results at CTAT and PTAT sensors.

|               | Non-calibrated<br>results | Calibrated results | Linearity<br>improvement | Overhead<br>area |

|---------------|---------------------------|--------------------|--------------------------|------------------|

| CTAT<br>0.64% | sensor                    | 1.32%              | 0.53%                    | 59.84%           |

| PTAT<br>1.08% | sensor                    | 10.47%             | 1.31%                    | 87.48%           |

Fig. 5. Die photo of the proposed CTAT and PTAT sensors.

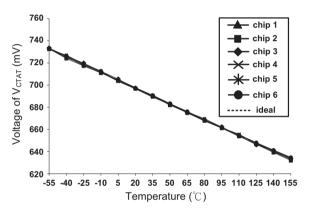

Fig. 6. Measurement results of the proposed CTAT sensor.

can be written as

$$\frac{I_{D1}}{I_{D4}} = \frac{\frac{W_2}{L_2}}{\frac{W_3}{L_3}} \tag{5}$$

$$\frac{\frac{1}{2}u(T)C_{\text{ox}}\frac{W_{1}}{L_{1}}[V_{\text{CS1}} - \text{Vth}(T)]^{2}}{\frac{1}{2}u(T)C_{\text{ox}}\frac{W_{4}}{L_{4}}[V_{\text{CS4}}(T) - \text{Vth}(T)]^{2}} = \frac{\frac{W_{2}}{L_{2}}}{\frac{W_{3}}{L_{3}}}$$

(6)

Based on Eqs. (5) and (6),  $V_{GS4}(T)$  can be written as

$$V_{\text{GS4}}(T) = \omega \times (V_{\text{GS1}} - \text{Vth0}) + \text{Vth0} + \Delta V_{\text{GS4}}(T)$$

(7)

where

$$\omega$$

is  $\sqrt{\frac{\frac{W_3}{L_2}}{\frac{V_2}{V_2}}} \times \frac{\frac{W_1}{L_1}}{\frac{W_4}{L_4}}$  and  $\Delta V_{\rm GS4}(T)$  is  $(\omega-1) \times \alpha(T-T_0)$ . If  $V_{\rm GS1}$  is a

constant value and  $\omega \approx$  1,  $\Delta V_{\rm GS4}(T)$  is almost equal to 0.  $V_{\rm GS4}(T)$  then almost becomes a constant as follows:

$$V_{\text{GS4}}(T) \cong \omega \times (V_{\text{GS1}} - \text{Vth0}) + \text{Vth0}$$

(8)

By Eqs. (2)–(4),  $I_{\text{sat}}(T)$  is derived as

$$I_{\text{sat}}(T) = \frac{1}{2}\beta_0[V_{\text{C}} + \alpha(T - T_0)]^2 \left(\frac{T}{T_0}\right)^{\text{UTE}}$$

(9)

where  $\beta_0$  is  $u_0 \times C_{ox} \frac{W}{L}$  and  $V_C$  is  $V_{GS4}(T)$  – Vth0. Then, we use Taylor series to approximate  $I_{sat}(T)$

$$I_{\text{sat}}(T) \cong I_0[1 + \eta(T - T_0) + \eta'(T - T_0)^2]$$

(10)

where  $I_0$  is  $\frac{1}{2}\beta_0V_{\rm C}^2$ ,  $\eta$  equals to  $\left(\frac{2\alpha}{V_{\rm C}} + \frac{2U\Pi{\rm E}}{596}\right)$ , and  $\eta'$  becomes  $\left(\frac{\alpha^2}{V_{\rm C}^2} + \frac{2\alpha U\Pi{\rm E}}{298V_{\rm C}} + \frac{2U\Pi{\rm E}(U\Pi{\rm E}-1)}{4\times 298^2}\right)$ . Notably,  $\eta$  and  $\eta'$  are negative coefficients. The best strategy to linearize Eq. (10) is to find a way to cancel the right-most term. Meanwhile, cost (area) is always a concern for the sensors to be physically used. Therefore, we utilize on-chip resistors, which also have a similar second-order effect vs. temperature, to carry out the cancellation of the right-most term in Eq. (10). The resistance vs. temperature variation of several n-well resistors is simulated in range of  $[-55^{\circ}{\rm C}; +155^{\circ}{\rm C}]$ , as shown in Fig. 2 and Table 1. The resistance characteristic of the n-well resistors, based on these simulations, can be approximated as

$$R(T) = R_0[1 + \gamma(T - T_0) + \gamma'(T - T_0)^2]$$

(11)

where  $R_0$  is the resistance of the n-well resistor at  $T_0$ , and  $\gamma$  and  $\gamma'$  are the first-order and the second-order temperature coefficients thereof, respectively. Thus,  $I_{\text{sat}}(T) \times R(T)$  is simplified as the following equation owing to the fact that  $\gamma$ ,  $\gamma'$ ,  $\eta$ , and  $\eta'$  are always very small

$$I_{\text{sat}}(T) \times R(T) \cong I_0 R_0 [1 + \eta (T - T_0) + \eta' (T - T_0)^2 + \gamma (T - T_0) + \gamma' (T - T_0)^2]$$

(12)

$\gamma$  and  $\gamma'$  of the 0.18 µm CMOS process are  $2.90\times10^{-3}$  and  $1.32\times10^{-5}$ , respectively, as shown in Table 1. According to Eqs. (8) and (9), if  $\omega$  is 1.2, Vref is 1.2 V, and Vth0 is 0.6 V,  $\eta$  and  $\eta'$  are derived as  $-4.02\times10^{-3}$  and  $-1.34\times10^{-5}$ , respectively. Thus,  $\gamma'$  is almost equal to  $-\eta'$  such that the second-order terms are canceled to linearized Vout(T). Thus, Eq. (12) is derived based on this assumption

$$I_{\text{sat}}(T) \times R(T) \cong I_0 R_0 [1 + \eta (T - T_0) + \gamma (T - T_0)]$$

(13)

$$Vout(T) = V_{GS4}(T) + I_0 R_0 [1 + \eta (T - T_0) + \gamma (T - T_0)]$$

(14)

The temperature coefficient of Vout(T) becomes as follows:

$$\frac{\partial}{\partial T}(\text{Vout}(T)) = I_0 R_0(\eta + \gamma) \tag{15}$$

Therefore, the output of the second-order calibrated temperature sensor, Vout(T), will become a first-order (linear) function vs. temperature.

In other words, by adjusting the resistance of the n-well resistor, an appropriate second-order positive temperature coefficient  $(\gamma')$  of the n-well resistor will be attained to cancel the second-order effects  $(\eta')$  of M4.

Besides, other major non-ideal effects of the second-order calibrated temperature sensor are channel length modulation and body effect. The channel length modulation affects the mismatch of the current mirror. Notably, adding the n-well resistor reduces the individual drain-source voltage drops of M3 and M4 such that the channel length modulation of M3 and M4 is suppressed. Besides, the substrates of all MOSs are connected to their individual own sources in the second-order calibrated temperature

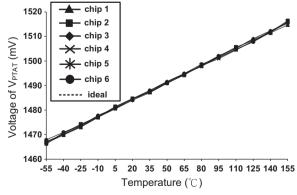

Fig. 7. Measurement results of the proposed PTAT sensor.

sensor. Thus, the body effect of the second-order calibrated temperature sensor will not be a problem. Besides, another serious problem is process variation, which causes various output offsets of those Vth-based temperature sensors given different processes [5–7,14,15,17,21]. Thanks to the linearity feature calibrated by the second order effect cancellation, we can apply the one-point calibration method to calibrate the output offsets of the proposed design at different process corners [17].

## 2.2. Second-order calibrated CTAT and PTAT sensors

Based on the previous second-order calibration method, the schematics of the second-order calibrated CTAT and PTAT sensors are shown in Fig. 3(a) and (b), respectively. According to Eq. (14),  $\eta$  and  $\gamma$  are negative and positive temperature coefficients, respectively. If  $|\eta| > |\gamma|$ , the output of the temperature sensor attains

Fig. 8. Error distribution of the proposed CTAT sensor.

$\textbf{Fig. 9.} \ \, \textbf{Error distribution of the proposed PTAT sensor.}$

**Table 3** Performance comparison of temperature sensors.

[6] [21] [22] The proposed CTAT sensor The proposed PTAT sensor [13] [16] Year 2012 2012 2013 2013 2013 2014 2014 Process (µm) 0.13 0.032 AMI 0.5 0.09SOI 0.16 0.18 0.18 Supply voltage (V) 1.65 1.5 1.8 1.8 1.8 5-100 -55 to 105 Temperature range (°C) 0-100 -40 to 100 -55 to 200 -55 to 155 -55 to 155 Inaccuracy (°C) -4/+4-1.95/+1.95-2.5/+2.5-3.5/+3.5-0.4/+0.4 $-3.73/+3.34^{a}$  $-3.73/+3.85^{a}$ 0.0125<sup>b</sup> 0.12 0.01 0.63 1.058 0.1 0.0074b Core area (mm<sup>2</sup>) Normalized temperature 0.08000 0.04105 0.03571 0.04375 0.00314 0.03376 0.03609 deviation

negative temperature characteristic and vice versa. The temperature characteristic of the second-order calibrated temperature sensor is given as follows.

If  $|\eta| > |\gamma|$ , it is the same as follows:

$$-\left(\frac{2\alpha}{(V_{\text{GS4}}(T) - \text{Vth0})} + \frac{2\text{UTE}}{596}\right) > \gamma \tag{16}$$

Eq. (16) is derived as follows based on Eq. (8).

$$\frac{1}{\omega} < \left(-\gamma - \frac{2\text{UTE}}{596}\right) \left(\frac{V_{\text{GS1}} - \text{Vth0}}{2\alpha}\right) \tag{17}$$

Therefore, the output of the second-order calibrated temperature sensor shows a negative temperature characteristic. By contrast, if  $|\eta| < |\gamma|$ , the equation becomes as follows:

$$\frac{1}{\omega} > \left(-\gamma - \frac{2\text{UTE}}{596}\right) \left(\frac{V_{\text{GS1}} - \text{Vth0}}{2\alpha}\right) \tag{18}$$

Thus, the output of the second-order calibrated temperature sensor attains a positive temperature coefficient. In summary, the second-order calibrated temperature sensor can be designed to possess either a negative or a positive temperature coefficient by adjusting  $\omega$ . Notably, the  $(-\gamma - \frac{2UTE}{596}) \binom{V_{CSI} - Vth0}{2\alpha}$  equals to 1.07. According to Eqs. (17) and (18), the valid  $\omega$  will be in the range between 0.9 and 1.2.

#### 3. Implementation and measurement results

In this work, the proposed CTAT and PTAT sensors are implemented using a typical 0.18 µm CMOS process. Fig. 4(a) and (b) shows the non-calibration and calibration simulation results of the proposed CTAT sensor, respectively, while Fig. 4(c) and (d) is those of the proposed PTAT sensor. Table 2 compares the non-calibrated and calibrated simulation results, where the maximum non-linearity reduction of the CTAT and PTAT sensors are 59.84% and 87.48%, respectively. Fig. 5 shows the die photo, where the core areas of the proposed CTAT and PTAT sensors is only 0.0125 mm<sup>2</sup> and 0.0074 mm<sup>2</sup>, respectively. The overhead area of the proposed CTAT and PTAT sensors are only 0.64% and 1.08%, respectively. Six different dies of the proposed CTAT and PTAT sensors are measured, as shown in Figs. 6 and 7, respectively. Figs. 8 and 9 summarize the deviation distributions of the proposed CTAT and PTAT sensors, respectively. In the range from  $-55^{\circ}$ C to 155 °C, the worst deviations of our CTAT and PTAT sensors are  $-3.75^{\circ}$ C to  $+3.34^{\circ}$ C and  $-3.73^{\circ}$ C to  $+3.85^{\circ}$ C, respectively. The performance comparison of the proposed design and several prior works is tabulated in Table 3. Among those designs to cover 100°C temperature sensing range, i.e., [13,6,21], and our works, our CTAT sensor and PTAT sensor attain the second smallest normalized temperature deviation and the fourth.

<sup>&</sup>lt;sup>a</sup> No any extra calibration points.

b Only temperature sensor.

$<sup>^{\</sup>rm c}$  Normalized temperature deviation= $\frac{{\rm lnaccuracy}}{{\rm Temperature\ range}}$

#### 4. Conclusion

The proposed CTAT and PTAT sensors are calibrated by using a current mirror and an n-well resistor to eliminate the second-order term of the temperature coefficient. Thus, the proposed CTAT and PTAT sensors can be used in a wide temperature range ( $-55\,^{\circ}\text{C}$  to  $155\,^{\circ}\text{C}$ ). The overhead area of the proposed CTAT and PTAT sensors, however, is only 0.64% and 1.08%, respectively. Besides, the same circuit architecture is used to carry out the CTAT and PTAT sensors to attain positive or negative temperature characteristics depending on the demand. Notably, the temperature range of proposed CTAT and PTAT sensors is currently known to be the widest to date.

## Acknowledgements

This investigation was partially supported by National Science Council, Taiwan, under Grants NSC102-2221-E-110-081-MY3 and NSC102-3113-P-110-010. The authors would like to express their deepest gratefulness to CIC (Chip Implementation Center) of NARL (Nation Applied Research Laboratories), Taiwan, for their thoughtful chip fabrication service.

#### References

- C.-C. Chung, C.-R. Yang, An autocalibrated all-digital temperature sensor for on-chip thermal monitoring, IEEE Trans. Circuits Syst. II, Exp. Briefs 58 (February (2)) (2011) 105–109.

- [2] FlexRay Communications System-Protocol Specification V2.1, 2005 (http://www.flexray.com).

- [3] A.-L. Aita, M.A.P. Pertijs, K.A.A. Makinwa, J.-H. Huijsing, G.C.M. Meijer, Low-power CMOS smart temperature sensor with a batch-calibrated inaccuracy of  $\pm$  0.25 °C (  $\pm$  3 $\sigma$ ) from -70 °C to 130 °C, IEEE Sens. J. 13 (May (5)) (2013) 1840–1848.

- [4] M.A.P. Pertijs, K.A.A. Makinwa, J.-H. Huijsing, A CMOS smart temperature sensor with a  $3\sigma$  inaccuracy of  $\pm$  0.1 °C from -55 °C to 125 °C, IEEE J. Solid-State Circuits 40 (December (12)) (2005) 2805–2815.

- [5] M. Law, A. Bermark, A 405-nW CMOS temperature sensor based on linear MOS operation, IEEE Trans. Circuits Syst. II, Exp. Briefs 56 (December (12)) (2009) 891–895.

- [6] L. Lu, B. Vosooghi, J. Chen, C. Li, A subthreshold-MOSFETs-based scattered relative temperature sensor front-end with a non-calibrated  $\pm 2.5\,^{\circ}\mathrm{C}\,3\sigma$  relative inaccuracy from  $-40\,^{\circ}\mathrm{C}$  to  $100\,^{\circ}\mathrm{C}$ , IEEE Trans. Circuits Syst. I, Reg. Pap. 60 (May (5)) (2013) 1104–1112.

- [7] A. Vaz, A. Ubarretxena, I. Zalbide, D. Pardo, H. Solar, A. Garcia-Alonso, R. Berenguer, Full passive UHF tag with a temperature sensor suitable for human body temperature monitoring, IEEE Trans. Circuits Syst. II, Exp. Briefs 57 (February (2)) (2010) 95–99.

- [8] D. Wolpert, P. Ampadu, A sensor system to detect positive and negative current-temperature dependences, IEEE Trans. Circuits Syst. II, Exp. Briefs 58 (April (4)) (2011) 235–239.

- [9] K. Woo, S. Meninger, T. Xanthopoulos, E. Crain, D. Ha, D. Ham, Dual-DLL based CMOS all-digital temperature sensor for microprocessor thermal monitoring, in: Proceedings of IEEE International Solid-State Circuits Conference, February 2009, pp. 68–69.

- [10] P. Chen, C.-C. Chen, C.-C. Tsai, W.-F. Lu, A time-to-digital converter-based CMOS smart temperature sensor, IEEE J. Solid-State Circuits 40 (August (8)) (2005) 1642–1648.

- [11] P. Chen, M.-C. Shie, Z.-Y. Zheng, Z.-F. Zheng, C.-Y. Chu, A fully digital time-domain smart temperature sensor realized with 140 FPGA logic elements, IEEE Trans. Circuits Syst. I, Reg. Pap. 54 (December (12)) (2007) 2661–2668.

- [12] P. Chen, C.-C. Chen, Y.-H. Peng, K.-M. Wang, Y.-S. Wang, A time-domain SAR smart temperature sensor with curvature compensation and a  $3\sigma$  inaccuracy of  $-0.4\,^{\circ}\text{C}$  to  $+0.6\,^{\circ}\text{C}$  over a  $0\,^{\circ}\text{C}$  to  $90\,^{\circ}\text{C}$  range, IEEE J. Solid-State Circuits 40 (March (3)) (2010) 600–609.

- [13] D. Ha, K. Woo, S. Meninger, T. Xanthopoulos, E. Crain, D. Ham, Time-domain CMOS temperature sensors with dual delay-locked loops for microprocessor thermal monitoring, IEEE Trans. Very Large Scale Integr. Syst. 20 (September (9)) (2012) 1590–1601.

- [14] C.-W. Lin, S.-F. Lin, A highly linear CMOS temperature sensor, in: Proceedings of IEEE Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (ECTI-CON), May 2011, pp. 74–77.

- [15] C. Zhao, J. He, S.-H. Lee, K. Peterson, R. Geiger, D. Chen, Linear Vt-based temperature sensors with low process sensitivity and improved power supply headroom, in: Proceedings of IEEE International Symposium on Circuits and Systems, May 2011, pp. 2553–2556.

- [16] G. Chowdhury, A. Hassibi, An on-chip temperature sensor with a self-discharging diode in 32-nm SOI CMOS, IEEE Trans. Circuits Syst. II, Exp. Briefs 59 (September (9)) (2012) 568–572.

- [17] Y. Jeong, F. Ayazi, Process compensated CMOS temperature sensor for microprocessor application, in: Proceedings of IEEE International Symposium on Circuits and Systems, May 2012, pp. 3118–3121.

- [18] K. Souri, Y. Chae, K.A.A. Makinwa, A CMOS temperature sensor with a voltage-calibrated inaccuracy of  $\pm$  0.15 °C ( $3\sigma$ ) from 55 °C to 125 °C, IEEE J. Solid-State Circuits 48 (January (1)) (2013) 292–301.

- [19] M.A.P. Pertijs, A.L. Aita, K.A.A. Makinwa, J.-H. Huijsing, Low-cost calibration techniques for smart temperature sensors, IEEE Sensors J. 10 (June (6)) (2010) 1098–1105.

- [20] R.-P. Fisk, S.M.R. Hasan, A calibration-free low-cost process-compensated temperature sensor in 130 nm CMOS, IEEE Sensors J. 11 (December (12)) (2011) 3316–3329.

- [21] L. Lu, S.T. Block, D.E. Duarte, C. Li, A 0.45-V MOSFETs-based temperature sensor front-end in 90 nm CMOS with a noncalibrated  $\pm$  3.5 °C 3 $\sigma$  relative inaccuracy from -55 °C to 105 °C, IEEE Trans. Circuits Syst. II, Exp. Briefs 60 (November (11)) (2013) 771–775.

- [22] K. Souri, K. Souri, K. Makinwa, A 40  $\mu$ W CMOS temperature sensor with an inaccuracy of  $\pm$  0.4 °C (3 $\sigma$ ) from -55 °C to 200 °C, in: Proceedings of the ESSCIRC, September 2013, pp. 221–224.

- [23] K. Souri, Y. Chae, F. Thus, K. Makinwa, A 0.85 V 600  $\mu$ W all-CMOS temperature sensor with an inaccuracy of  $\pm$  0.4 °C (3 $\sigma$ ) from -40 to 125 °C, in: Proceedings of IEEE International Solid-State Circuits Conference Digest of Technical Papers, February 2014, pp. 222–223.

- [24] C. Azcona, B. Calvo, N. Medrano, S. Celma, CMOS quasi-digital temperature sensor for battery operated systems, IEE Electron. Lett. 49 (October (21)) (2013) 1338–1340.

- [25] C. Azcona, B. Calvo, N. Medrano, S. Celma, Low-power wide-range frequencyoutput temperature sensor, IEEE Sens. J. 14 (May (5)) (2014) 1339–1340.

- [26] C. Azcona, B. Calvo, N. Medrano, S. Celma, 1.2 V–0.18 mm CMOS temperature sensors with quasi-digital output for portable systems, IEEE Trans. Instrum. Meas. (2015) (available on line). http://dx.doi.org/10.1109/TIM.2015.2408804.