# A Voltage Monitoring IC With HV Multiplexer and HV Transceiver for Battery Management Systems

Chih-Lin Chen, *Student Member, IEEE*, Deng-Shian Wang, Jie-Jyun Li, and Chua-Chin Wang, *Senior Member, IEEE*

Abstract—This paper presents a voltage monitoring IC with high-voltage multiplexer (HVMUX) and HV transceiver for battery interconnect module (BIM) used in battery management systems (BMSs). The voltage monitoring IC must be able to accommodate input voltage up to tens of volts, perhaps even hundreds of volts, which is difficult to be realized using a logic-based solution. To realize a solution on silicon, the voltage monitoring IC shall be fabricated using an advanced HV semiconductor process, which usually is constrained by the voltage drop limitation between gate and source of HV devices. To overcome such a limitation, an HV switch is proposed in this paper, including an HV gate voltage driver (HVGVD) driving the HV MOS without any over-voltage hazard. In addition, an HV transceiver is proposed using CMOS transistors without any isolator. An experimental prototype is fabricated using a typical 0.25  $\mu$ m 1-poly 3-metal 60 V BCD process. The measurement results reveal that the error and off-isolation of HVMUX is less than 2.54% and -92 dB@1 MHz, respectively. Meanwhile, the HV transceiver can transmit and receive data with a  $-32 \sim +32$  V common voltage.

Index Terms—Analog high-voltage multiplexer (HVMUX), battery management system (BMS), high voltage (HV), high voltage transceiver.

## I. INTRODUCTION

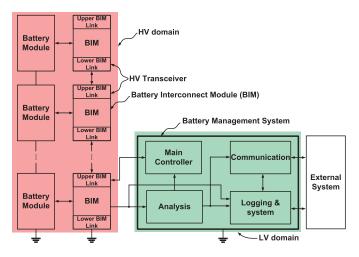

IGH-VOLTAGE (HV) battery management system (BMS) is widely needed in many applications, e.g., electric vehicle and hybrid electric vehicle, where many battery modules are assembled and integrated. One of the popular BMS architectures is the modular formation, i.e., a module monitors several batteries with a daisy-chain interface. For example, a distributed BMS is composed of at least five blocks, including battery interconnect modules (BIM), main

Manuscript received August 8, 2013; revised December 9, 2013; accepted January 22, 2014. This work was supported in part by the Metal Industries Research Development Centre; Ministry of Economic Affairs, Taiwan, under Grant 102-EC-17-A-01-01-1010, Grant 99-EC-17-A-01-S1-104, and Grant 99-EC-17-A-19-S1-133; in part by the National Science Council of Taiwan under Grant NSC101-3113-P-110-004 and Grant NSC102-2917-I-110-003; and in part by the Southern Taiwan Science Park Administration, Taiwan, under Contract EI-28-05-10-101. (Corresponding author: C.-C. Wang.)

The authors are with Department of Electrical Engineering, National Sun Yat-Sen University, Kaohsiung 80424, Taiwan (e-mail: clchen@vlsi.ee.nsysu.edu.tw; tonyhenry2@vlsi.ee.nsysu.edu.tw; future@vlsi.ee.nsysu.edu.tw; ccwang@ee.nsysu.edu.tw).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TVLSI.2014.2303989

Fig. 1. Explosive view of a typical distributed BMS.

controller, analysis, communication, and logging and telemetry, as shown in Fig. 1 [1], [2]. In addition to BIMs, the other four blocks are operated in low voltage (LV) domain. BIM is in charge of detecting the battery status by HV multiplexer (HVMUX), e.g., voltage, current, and temperature. Meanwhile, these battery information can be transmitted/received between adjacent BIMs by HV transceiver (upper BIM link and lower BIM link). Due to the recent HV process availability, each BIM can monitor more and more batteries. Notably, the communication methods between adjacent BIMs are realized with or without discrete components, e.g., opto-coupler [3], [4].

Several HVMUXs and HV switches have been reported [5]–[9]. A 2 × VDD switch was proposed using a conventional 0.18  $\mu$ m CMOS process [5], [6]. However, the switch in these reports only has 7-V tolerance, it is not possible to be used in a large scale HV BMS. An 32 × 32 channel multiplexer was fabricated with a 0.35  $\mu$ m silicon on insulator (SOI) process to apply in an ultrasound imaging system [7]. For field applications, the input voltage must be close to 0 V before the multiplexer is turned off. However, the batteries in BMS are always connected to BIM such that the input voltage of the multiplexer is impossible to be 0 V. Therefore, the multiplexer cannot be turned off completely, and cause a significant voltage error during voltage measurement. It is then not a good option for

BMS designs. An integrated HVMUX was fabricated with a 0.35  $\mu$ m 50-V CMOS process [8], where a large floating gate drive voltage in the HV switch ( $\approx$ 15 V) was generated directly due to the voltage drop over the resistor. Therefore, it could result in a leakage current flowing into the output and causing large voltage distortion. A 16:1 analog MUX was revealed using a combination of process (CMOS/SOI) techniques [9], where 5-V CMOS logic circuits are shifted up to  $\pm$ 15 V to drive HV analog switches. Referring to technology considerations for automotives [10], the SOI technology is not welcomed for power devices, since the thermal conductivity of the oxide is very low. In addition, the SOI technology is quite expensive and the integration is not very easy and straightforward, e.g., vertical components and ESD protection cells.

Another critical issue in the BMS is to the data communication among BIMs by HV transceivers or digital isolators. They are usually implemented by discrete devices, e.g., optocoupler, magnetic isolator, and capacitive isolator. Several HV transceivers or digital isolators have been reported [3], [4], [11]-[16]. An optical coupler is used to isolate and communicate between HV and LV systems [3], [4]. The disadvantages of optical couplers are high power consumption, poor integration, low speed, and degradation of light emitting diode (LED). Digital isolators using magnetic coupling [11]–[13] or capacitive coupling [14], [15] methods were proposed. However, no matter magnetic or capacitive coupling transmissions, they will generate electromagnetic interference (EMI) effect to jam other circuits or be corrupted by external wireless signals to endanger the reliability. In addition, they usually use a lot of discrete components, i.e., transformer and capacitor. Therefore, it is not easily integrated in systemon-chip (SoC) designs. A wireless battery monitor was also proposed [16]. However, it is not cost effective to realize a large scale battery system because it needs a lot of wireless modules. In other words, the cost and area efficiency will be problems.

Recently, many advanced semiconductor processes have been proposed to fabricate HV devices on silicon, e.g., TSMC  $0.25 \mu m$  1-poly 3-metal 60-V BCD process [17], [18]. This particular process offers digital cell library, LV MOSs driven by 2.5 V/5 V, and several types of HV MOS devices. Especially, the BCD technology with high power capabilities (BiCMOS technology) and integration feasibility between analog and digital devices (CMOS technology) is considered a better solution. Furthermore, the BCD technology also provide better area efficiency [19], where low voltage devices are widely used as much as possible and many external components are able to be implemented on silicon. The most critical limitation, however, is that the gate to source voltage of the HV MOS transistor must be limited under a LV  $\approx$ 5 V. Therefore, those mentioned prior works are not easy to be directly implemented using this HV BCD process.

In this paper, we propose novel HVMUX and HV transceiver to resolve all the mentioned problems. In Section II, we explain the specifications of HVMUX and HV transceiver. In Section III, the HVMUX is disclosed, including HV switch

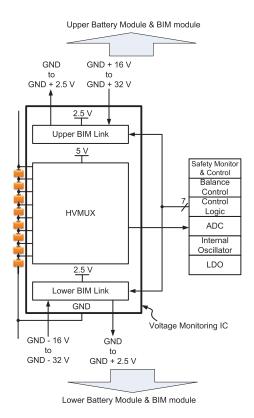

Fig. 2. Block diagram of BIM.

and HV gate voltage driver (HVGVD). For field applications, HVMUX converts the voltage drop of each battery in the same string into the input range of an analod-to-digital converter (ADC). In Section IV, the schematic of HV transceiver is shown and analyzed. Notably, the proposed HV transceiver can transmit and receive data with -32 to +32 V common voltage. In Section V, we demonstrate the measurement results of the proposed HVMUX and HV transceiver. The performance comparison between our design and several prior works is also discussed. Finally, a brief conclusion is given in Section VI.

## II. BIM SYSTEM SPECIFICATIONS

A conceptual architecture of BIM is shown in Fig. 2, where voltage monitoring IC is composed of HVMUX and HV transceiver (upper BIM link and lower BIM link). The ADC is used to convert the output of HVMUX into a digital code, which will be passed via a serial link to HV transceiver by control logic to communicate with main controller in Fig. 1 [20]. Notably, the HVMUX and HV transceiver is operated in HV domain. The HVMUX is in charge of down-converting HV of each battery into the input range of the corresponding ADC. According to voltage measurement approaches [1], using the HVMUX is deemed as a better solution to save power and area, because each battery cell is not parallelly coupled to a corresponding ADC. Notably, a differential approach in HVMUX is good for autocancelling the common noise. The bottom line of such a design is that the voltage distortion caused by the HVMUX must be as small as possible.

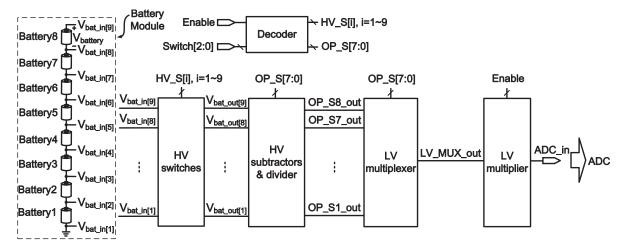

Fig. 3. Schematic of 8:1 analog HVMUX.

For example, the voltage range of each battery is around 2–4 V. Therefore, the input range of HVMUX is from 2 to 32 V. HV switches in HVMUX should possess voltage tolerance up to maximum 32 V, which will be introduced and explained in Section III. In addition, if each transmitter in HV transceiver transmits data between GND +2.5 V and GND level, the receiver in upper BIM link must receive the voltage range between GND +16 and GND +32 V, where 16 and 32 V mean that all batteries are operated in 2 or 4 V, respectively. By contrast, the receiver in lower BIM link must receive the voltage range between GND –16 and GND –32 V. In short, our HV transceiver can exchange data with a –32 to +32 V common voltage to meet the mentioned system signal requirements, which will be introduced and explained in Section IV.

## III. HV MULTIPLEXER

The proposed 8:1 analog HVMUX is shown in Fig. 3, including HV switches, HV subtractors and divider, LV multiplexer (LVMUX), and LV multiplier. The HVMUX selects a pair of input voltages, e.g.,  $V_{\rm bat\_in[1]}$  and  $V_{\rm bat\_in[2]}$ , and passes them to ADC, namely ADC\_in. Switch[2:0] selects one battery in battery module to be sensed. Notably, the decoder converts Switch[2:0] into HV\_S[i], i = 1-9 and OP\_S[7:0] to drive the HV switches, HV subtractors and divider, and LVMUX. Enable is used to turn on or off the HVMUX for power saving. Take an example to acquire the voltage of Battery8 ( $V_{\rm battery}$ ).

- 1) First, Switch[2:0] is set to 111.

- 2) The top and bottom of Battery8 ( $V_{\text{bat\_in[9]}}$  and  $V_{\text{bat\_in[8]}}$ ) are selected to HV subtractors and divider by HV switches.

- 3) Because the OTA in HV subtractors and divider is LV domain,  $V_{\text{bat\_in}[9]}$  and  $V_{\text{bat\_in}[8]}$  must be scaled down by eight. In other words, the difference of  $V_{\text{bat\_in}[9]}$  and  $V_{\text{bat\_in}[8]}$  ( $V_{\text{battery}}$ ) is also scaled down by eight.

- 4) Finally, the LV multiplier is used to restore the  $V_{\rm battery}$ . The function description of each block of HVMUX is given in the following text.

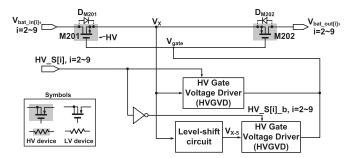

Fig. 4. Schematic of HV switch cell.

#### A. HV Switches

The HV switches are composed of eight HV switch cells, where each HV switch cell comprises M201, M202, level-shift circuit, HVGVD, and an inverter, as shown in Fig. 4. M201 and M202 are HV devices.  $D_{M201}$  and  $D_{M202}$  are parasitic diodes of M201 and M202, respectively. Notably,  $|V_{\rm gs}|$  of the HV devices must be smaller than 5 V. In other words, the voltage difference between  $V_X$  and  $V_{\rm gate}$  must be clamped under 5 V. When  $V_{\rm gate}$  is equal to  $V_X$ , M201 and M202 are turned off. By contrast, when  $V_{\rm gate}$  is equal to  $V_X - 5V$ , M201 and M202 are turned on. The level-shift circuit is used to generate  $V_X - 5V$ , namely  $V_{X-5}$ . Referring to Fig. 4, the HV switch is driven by HV\_S[i], i = 2–9, which chooses  $V_{\rm gate} = V_X$  or  $V_{\rm gate} = V_{X-5}$  by HVGVD. Therefore, M201 and M202 are protected from any over-voltage hazard.

# B. HV Gate Voltage Driver

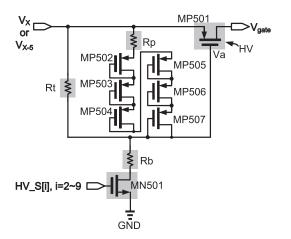

Fig. 5 shows the schematic of HVGVD, including three HV resistors ( $R_t$ ,  $R_b$ , and  $R_p$ ), MN501, and MP501 – MP507, where MN501 and MP501 are HV devices. Again,  $|V_{\rm sg}|$  of the HV devices must be smaller than 5 V. The  $V_{\rm sg}$  of MN501 is driven by HV\_S[i], i=2–9, which is a digital signal. Therefore, MN501 is ensured without any over-voltage hazard. To prevent the over-voltage damage of MP501, the voltage difference between  $V_X$  and  $V_a$  must be smaller than 5 V. Because  $V_a$  is derived from  $V_X$ , the voltage range of  $V_X$  is

Fig. 5. Schematic of HVGVD.

analyzed in two scenarios, i.e., LV mode ( $V_X \le 5$  V) and HV mode ( $V_X > 5$  V).

In HV mode,  $V_a$  is clamped by  $R_p$  and MP502–MP507. In other words,  $V_a$  is constrained by following:

$$V_a = V_X - (V_{R_p} + 6 \times |V_{\text{thp}}|) \tag{1}$$

where  $V_{R_p}$  is the voltage drop of  $R_p$ , and  $|V_{\text{thp}}|$  is the threshold voltage of MN502–MN507. The  $V_{\text{sg}}$  of MP501 is then written as follows:

$$V_{\text{sg}} \text{ of MP501} = V_{R_p} + 6 \times |V_{\text{thp}}| < 5 \text{ V}$$

(2)

where  $V_{R_p}$  is negligible because  $R_p$  is used to limit the peak current from  $V_X$  such that the MP502–MP507 are protected from large current hazards.

In LV mode,  $V_a$  is generated by  $R_t$  and  $R_b$ . Assumed  $R_t$  is equal to  $R_b$ ,  $V_a$  is the half of  $V_X$ . Thus,  $V_{\rm sg}$  of MP501 is half of  $V_X$  ( $\leq$ 2.5 V). Therefore, MP501 is also ensured without any over-voltage hazard.

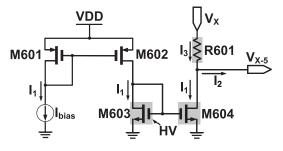

## C. Level-Shift Circuit

Level-shift circuit is composed of a current source,  $I_{\text{bias}}$ , two current mirrors, M601–M604, and a load resistor, R601, as shown in Fig. 6. Current source,  $I_{\text{bias}}$ , and M601 and M602 are LV devices. M603, M604, and R601 are HV devices. Levelshift circuit generates  $V_{X-5}$ , which can be constrained by the following:

$$V_{X-5} = V_X - R601 \times I_3 \tag{3}$$

where  $I_3$  is the current through R601. Assume the voltage difference between  $V_X$  and  $V_{X-5}$  is equal to 5 V, R601 can be written as

$$R601 = \frac{5}{I_3} = \frac{5}{I_1 + I_2} \tag{4}$$

where  $I_1$  is the drain current of M604, which is supplied by the  $I_{\text{bias}}$ ,  $I_2$  is the input current of HVGVD. Referring to Fig. 5,  $I_2$  can be derived as

$$I_2 = \frac{V_X}{R_t + R_b + R_{o\text{MN501}}} \tag{5}$$

Fig. 6. Schematic of level-shift circuit.

Fig. 7. Schematic of HV subtractors and divider.

where  $R_{oMN501}$  is the output resistor of MN501. Substituting (5) into (4), R601 can be found as

$$R601 = \frac{5}{I_1 + \frac{V_X}{R_t + R_b + R_{oMN501}}}.$$

(6)

Equation (6) shows how to calculate the device parameter of R601, where  $I_1$ ,  $R_t$ ,  $R_b$ , and  $R_{o \text{MN}501}$  can be determined based on the limitation of power dissipation.

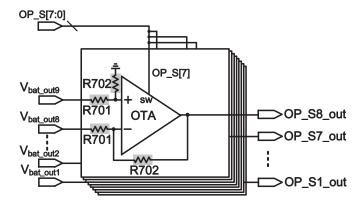

# D. HV Subtractors and Divider

Fig. 7 shows the schematic of HV subtractors and divider composed of an operational transconductance amplifiers (OTA), R701, and R702, where R701 and R702 can be selected based on the voltage and current tolerance.

Take  $V_{\text{battery}}$  in Fig. 3 as an example, it can be derived as follows:

$$V_{\text{battery}} = \frac{R_{702}}{R_{701}} \times (V_{\text{bat\_in}[9]} - V_{\text{bat\_in}[8]})$$

(7)

where  $(V_{\text{bat\_in[9]}} - V_{\text{bat\_in[8]}})$  is the voltage drop of the first battery on the top, while the ratio of  $R_{702}$  and  $R_{701}$  is utilized to shift the voltage of this battery into a lower voltage range.

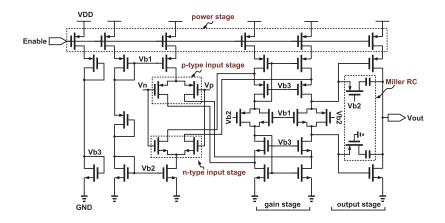

A rail-to-rail amplifier topology [21] is adopted to implement the OTA in Fig. 7. The detailed schematic of the OTA is shown in Fig. 8. The input pairs, i.e., n-type and p-type input stages, allow a wide input range. The gain stage use a cascode architecture to boost the gain. The Miller resistors and capacitors in the output stage are in charge of phase compensation. The n-type and p-type common source

Fig. 8. Schematic of OTA.

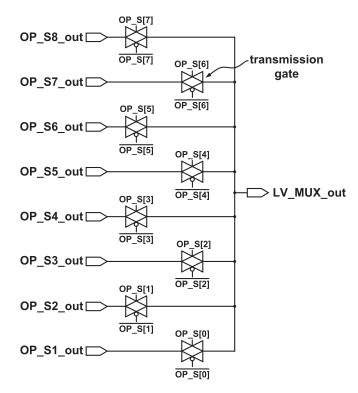

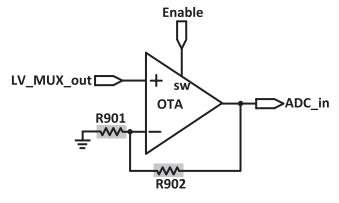

Fig. 9. Schematic of LVMUX.

Fig. 10. Schematic of LV multiplier.

amplifiers (output stage) are used to enlarge output voltage range. In addition, enable pin is the power gating signal to activate the entire OTA for the sake of power saving.

Fig. 11. Floorplan of HV transceiver.

# E. LVMUX and LV Multiplier

LVMUX in Fig. 3 is composed of eight transmission gates, which are, respectively, driven by OP\_S[0]–OP\_S[7], as shown in Fig. 9. LVMUX selects one of OP\_S8\_out–OP\_S1\_out to be LV\_MUX\_out. The last stage in Fig. 3 is LV multiplier, as shown in Fig. 10. LV multiplier multiplies the voltage at LV\_MUX\_out with  $R_{902}/R_{901}$  to generate a scaled output voltage, ADC\_in, for the following ADC in Fig. 2:

$$ADC_{in} = \left(1 + \frac{R_{902}}{R_{901}}\right) \times LVMUX_{out}$$

(8)

TABLE I FUNCTIONALITIES OF HV TRANSCEIVER

| Name | Functionality                                                             |

|------|---------------------------------------------------------------------------|

| TX_H | BIM transmits data (TXD_H) to upper BIM by CHP2_U and CHN2_U.             |

| RX_H | BIM receives differential signals (CHP2_D and CHN2_D) from the upper BIM. |

| TX_L | BIM transmits data (TXD_L) to lower BIM by CHP1_D and CHN1_D.             |

| RX_L | BIM receives differential signals (CHP1_U and CHN1_U) from the lower BIM. |

Fig. 12. Schematic of TX\_H and TX\_L [22].

where  $R_{902}$  and  $R_{901}$  are used to adjust the LV\_MUX\_out into the voltage range of ADC, and LV\_MUX\_out is the output voltage of LVMUX.

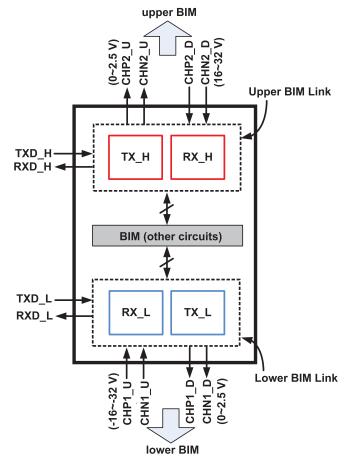

## IV. HV TRANSCEIVER

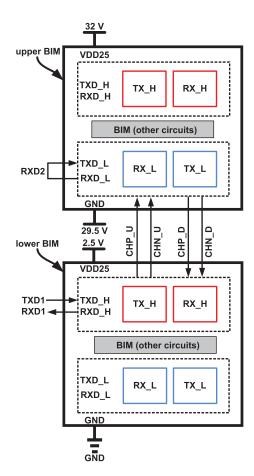

Referring to Figs. 1 and 2 again, HV transceiver is composed of upper BIM link and lower BIM link, as shown in Fig. 11. Upper BIM link is used to communicate with the upper adjacent BIM by TX\_H and RX\_H. By contrast, lower BIM link is in charge of communicating with the lower adjacent BIM by TX\_L and RX\_L. The functionalities of HV transceiver are summarized in Table I. Notably, RX\_H must receive positive HV signals (assumed using in a series of eight batteries and common voltage is 16–32 V) from the upper adjacent BIM, and RX\_L receive negative HV signals (common voltage: -16 to -32 V) from the lower adjacent BIM.

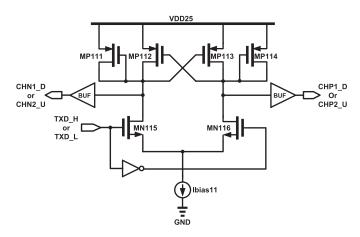

# A. TX\_H and TX\_L

The two transmitters, TX\_H and TX\_L, are used to transfer data to upper and lower adjacent BIMs at the same time. Therefore, they are realized using same circuits to convert TXD\_H (or TXD\_L) to CHN1\_D and CHP1\_D (or CHN2\_U and CHP2\_U), as shown in Fig. 12 [22], where BUF is a buffer to supply a large drive current. Referring to Fig. 12, M111-M114 consists of a cross coupling and positive feedback loop to speed up the transition. In addition, it can decrease the phase delay between CHN1\_D and CHP1\_D (or CHN2\_U and CHP2\_U). Most important of all, the voltage swing of all outputs is from VDD25 (2.5 V) to GND (0 V) for control logic.

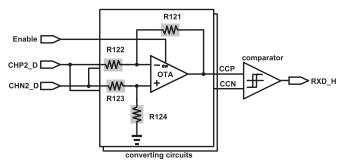

Fig. 13. Schematic of RX\_H.

# B. RX\_H and RX\_L

To receive data from upper and lower adjacent BIMs, the two receivers, RX\_H and RX\_L, must convert the positive and negative HV signals (16–32 V and –16 to –32 V) into 0–2.5 V. Notably, they are equipped with HV tolerance. Fig. 13 shows the schematic of RX\_H, including two converting circuits and a comparator with hysteresis [23]. The converting circuit has to convert the CHP2\_D and CHN2\_D into the input range of the following comparator. Each converting circuit consists of OTA, R121–R124, generating CCP and CCN voltage references. CCP is constrained by the following:

CCP = CHN2\_D ×

$$\frac{R124}{R123 + R124}$$

×  $\left(1 + \frac{R121}{R122}\right)$

-CHP2\_D ×  $\frac{R121}{R122}$  (9)

where the first term at the right hand is adjusted as a common voltage. The conversion function is based upon the linear mapping from 16–32 to 0–2.5 V such that the ratios of R121/R122 and R124/R123 can be easily calculated. Similar to CCP, CCN is also derived. Therefore, the comparator can compare CCP with CCN to generate RXD\_H. Assumed R122 and R123 are more than 10 times of R121 and R124. RXD\_H can be rewritten as

RXD\_H =

$$A_o \times (\text{CHP2\_D} - \text{CHN2\_D})$$

$\times \left(\frac{R121}{R122} + \frac{R124}{R123}\right)$  (10)

where  $A_o$  is the dc gain of the comparator and is far larger than the last term (R121/R122 + R124/R123). Therefore, when CHP2\_D is larger than CHN2\_D, RXD\_H is pulled high as logic 1. By contrast, when CHP2\_D is lower than CHN2\_D, RXD H is pulled low as logic 0.

7

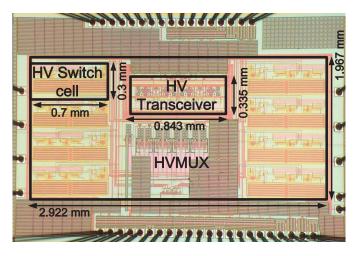

Fig. 14. Die photo of the proposed design.

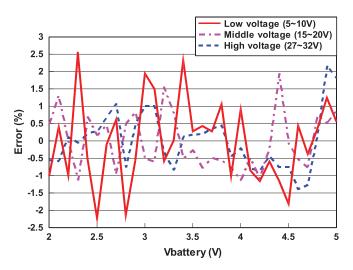

Fig. 15. Error distribution given three different input range of HVMUX.

By contrast, RX\_L is in charge of converting negative HV signals from (-16 to -32 V) into (0 to 2.5 V). The schematic of RX\_L is similar to that of RX\_H. Notably, the output of RX L is RXD L, as shown in Fig. 11.

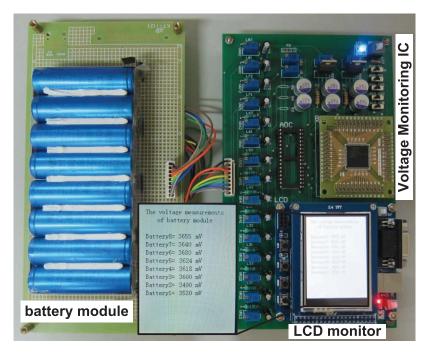

#### V. IMPLEMENTATION AND MEASUREMENT

The proposed design is implemented using 0.25  $\mu$ m 1-poly 3-metal 60 V BCD process to justify the performance. Fig. 14 shows the die photo of the proposed voltage monitoring IC on silicon. The core area is 2.922  $\times$  1.967 mm<sup>2</sup>, where the area of one HV transceiver and one HV switch cell are 0.843  $\times$  0.335 and 0.7  $\times$  0.3 mm<sup>2</sup>, respectively.

Fig. 15 shows the error distribution of HVMUX given three different input ranges, where  $V_{\text{battery}}$  is voltage of battery from 2 to 5 V. These input ranges are described as follows.

- 1) LV (5-10 V): lower range of input voltage range in HVMUX.

- 2) Middle voltage (15–20 V): typical range of input voltage range in HVMUX.

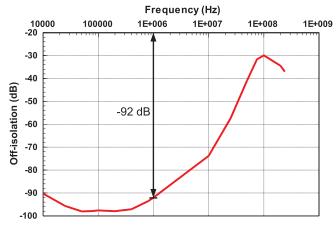

Fig. 16. Measurement results of off-isolation of HVMUX.

Fig. 17. Measurement configuration of the proposed HV transceiver.

3) HV (27–32 V): upper range of input voltage range in HVMUX.

The worst-case error of HVMUX is less than  $\pm 2.54\%$ . Fig. 16 shows the off-isolation of HVMUX. Given a normal 1 MHz data rate, the performance of off-isolation achieves -92 dB. Therefore, the proposed HVMUX will not be contaminated by digital control logic signals in Fig. 2.

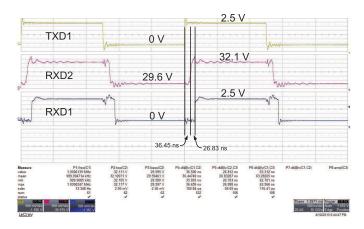

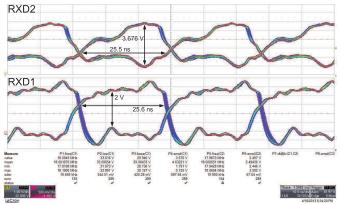

The measurement setting of the proposed HV transceiver is shown in Figs. 17 and 18. TXD1 is the input data. The lower BIM transmits data to the upper BIM by CHP\_U

Fig. 18. Photo of the measurement prototype with the proposed voltage monitoring IC.

Fig. 19. Measurement results of HV transceiver.

Fig. 20. Eye diagrams of HV transceiver given 70 Mb/s data rate (maximum) from lower BIM to upper BIM.

and CHN\_U. The upper BIM receives the data to generate RXD2, and then it transmits the data to the lower BIM. Finally, the lower BIM receives the data to generate RXD1.

Fig. 21. Eye diagrams of HV transceiver given 36 Mb/s data rate (maximum) from upper BIM to lower BIM.

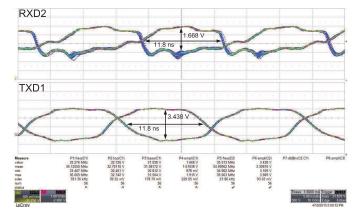

All of the measurement results are shown in Fig. 19. All of these signals, TXD1, RXD2, RXD1, should demonstrate the same logic values, except the delays there between. The propagation delays are 36.45 and 26.83 ns, respectively. The eye diagrams of HV transceiver given maximum data rates are also measured, as shown in Figs. 20 and 21. The maximum date rate from TX\_H to RX\_L and from TX\_L to RX\_H are 70 and 36 Mb/s, respectively.

The performance of the proposed HVMUX and HV transceiver is summarized and compared with several prior works in Tables II and III. Referring to Table II, our proposed HVMUX without SOI technology attains the second best isolation,  $-92~\mathrm{dB@1~MHz}$ . Referring to Table III, the proposed HV transceiver achieves the second best propagation delay and power dissipation. Most important of all, no isolator nor any discrete (opto-couplers) is needed in our proposed HV transceiver.

18.781 mW

$3.45 \text{ mm}^2$

17.79 mW

$1.95 \text{ mm}^2$

| Specifications     | This work                                | [7]                      | [9]            | [8]                                              | [17]                                            |

|--------------------|------------------------------------------|--------------------------|----------------|--------------------------------------------------|-------------------------------------------------|

| Year               | 2013                                     | 2005                     | 2008           | 2011                                             | 2012                                            |

| Results            | Measured                                 | Measured                 | Measured       | Measured                                         | Post-sim                                        |

| Process $(\mu m)$  | $0.25~\mu\mathrm{m}$ $60~\mathrm{V}$ BCD | $0.35~\mu\mathrm{m}$ SOI | 30 V CMOS/SOI  | $0.35~\mu\mathrm{m}~50~\mathrm{V}~\mathrm{CMOS}$ | $0.25~\mu\mathrm{m}~60~\mathrm{V}~\mathrm{BCD}$ |

| Number of switches | 8                                        | $32\times32$             | 16             | 4                                                | 8                                               |

| Analog input range | 4∼32 V                                   | -40∼40 V                 | -5∼25 V        | 0~40 V                                           | 2~29.2 V                                        |

| Isolation          | -92 dB@1 MHz                             | -53 dB@4 MHz             | -45 dB@0.2 MHz | -90 dB@10 MHz                                    | -79.4 dB@10 MHz                                 |

10 mW/switch

N/A

TABLE II COMPARISON BETWEEN THE PROPOSED HVMUX AND PRIOR WORKS

TABLE III COMPARISON BETWEEN THE PROPOSED HV TRANSCEIVER AND PRIOR WORKS

<15 mW

N/A

| Specifications                      | This work                     | [3]             | [14]                    | [12]                          |

|-------------------------------------|-------------------------------|-----------------|-------------------------|-------------------------------|

| Year                                | 2013                          | 2003            | 2005                    | 2012                          |

| Results                             | Measured                      | Measured        | Measured                | Measured                      |

| Process $(\mu m)$                   | $0.25~\mu\mathrm{m}$ 60 V BCD | GaAs & BiCMOS   | SOI                     | 5V CMOS                       |

| Maximum data rate                   | 70 Mbps                       | 25 Mbps         | 1 Mbps                  | 250 Mbps                      |

| Communication between adjacent BIMs | 4 wires                       | 2 wires         | 4 wires                 | 4 wires                       |

| Number of isolator                  | 0                             | 2 opto-couplers | 4 capacitors            | 2 transformers                |

| Propagation delay                   | 26.83~36.45 ns                | >40 ns          | $30 \sim 80 \text{ ns}$ | 5.5 ns                        |

| Power dissipation                   | 10.1 mW                       | 20~100 mW       | 40 mW                   | 8 mW                          |

| Area                                | $0.282 \text{ mm}^2$          | N/A             | N/A                     | $0.12~\mathrm{mm}^{2\dagger}$ |

|                                     | $2\times(Tx \& Rx)$           |                 |                         | (Tx & Rx)                     |

<sup>(†)</sup> Not include the area between Tx and transformer

## VI. CONCLUSION

Power dissipation

Area

In this paper, we propose a total HV solution on silicon for BIMs. The proposed design is implemented using a typical  $0.25 \mu m$  1-poly 3-metal 60-V BCD process such that it can be easily integrated in a possible SoC solution for BMS. The measurement results justify our design to be a high performance analog HV multiplexer (HVMUX) with HV transceiver. The error of the proposed HVMUX is smaller than 2.54% from 5 to 32 V, as shown in Fig. 15. In addition, the off-isolation of HVMUX is -92 dB@1 MHz. Lastly and most importantly, the proposed HV transceiver does not need additional discrete components and isolators.

## ACKNOWLEDGMENT

The authors would like to thank Chip Implementation Center (CIC) of Nation Applied Research Laboratories (NARL), Taiwan, for their thoughtful chip fabrication service.

## REFERENCES

- [1] D. Andrea, Battery Management Systems for Large Lithium-Lon Battery Packs, Norwood, MA, USA: Artech House, 2010, pp. 47-52.

- [2] M. Kultgen, "Managing high-voltage lithium-ion batteries in HEVS," Inf., News, Bus. Strategy Electron. Des. Eng., vol. 54, no. 7, pp. 45-52, Apr. 2009.

- [3] R. Kliger, "Integrated transformer-coupled isolation," IEEE Instrum. Meas. Mag., vol. 6, no. 1, pp. 16-19, Mar. 2003.

- [4] C.-H. Hsu, K.-C. Chang, Y.-C. Ou, K.-Y. Liao, and C.-L. Wey, "On the implementation of CAN buses to battery management systems," in *Proc.* IEEE Int. Midwest Symp. Circuits Syst., Aug. 2011, pp. 1-4.

- [5] E. K. F. Lee, "High-voltage tolerant stimulation monitoring circuit in conventional CMOS process," in Proc. Custom Integr. Circuits Conf., Sep. 2009, pp. 93-96.

- [6] K. P. Ng, M. C. Lee, W. T. Chan, R. Barsatan, and M. Chan, "Universal high voltage multiplexer for CMOS OTP memory applications," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits, Dec. 2008, pp. 1-4.

[7] K. Hara, J. Sakano, M. Mori, S. Tamano, R. Sinomura, and K. Yamazaki, "A new 80V 32×32ch low loss multiplexer LSI for a 3D ultrasound imaging system," in Proc. Int. Symp. Power Semicond. Devices ICs, May 2005, pp. 359-362.

N/A

N/A

- [8] J. Borg and J. Johansson, "An ultrasonic transducer interface IC with integrated push-pull 40 Vpp, 400 mA current output, 8-bit DAC and integrated HV multiplexer," IEEE J. Solid-State Circuits, vol. 46, no. 2, pp. 475-484, Feb. 2011.

- [9] D. A. Adams, H. A. Barnes, M. D. Fitzpatrick, N. P. Goldstein, W. L. Hand, W. L. Jackson, et al., "A radiation hardened high voltage 16:1 analog multiplexer for space applications (NGCP3580)," in Proc. IEEE Radiation Effects Data Workshop, Jul. 2008, pp. 82-84.

- [10] H. Casier, P. Moens, and K. Appeltans, "Technology considerations for automotive," in Proc. Eur. Solid-State Circuits Conf., Sep. 2004, pp. 37-41.

- [11] S. Wayne, "iCoupler digital isolators protect RS-232, RS-485, and CAN buses in industrial, instrumentation, and computer applications," Analog Dialogue, vol. 39, pp. 1-4, Oct. 2005.

- [12] S. Kaeriyama, S. Uchida, M. Furumiya, M. Okada, T. Maeda, and M. Mizuno, "A 2.5 kV isolation 35 kV/us CMR 250 Mbps digital isolator in standard CMOS with a small transformer driving technique," IEEE J. Solid-State Circuits, vol. 47, no. 2, pp. 435-443, Feb. 2012.

- M. Brandl, H. Gall, M. Wenger, V. Lorentz, M. Giegerich, F. Baronti, et al., "Batteries and battery management systems for electric vehicles," in Proc. Des., Autom. Test Eur. Conf. Exhibit., Mar. 2012, pp. 971-976.

- [14] M. Kikuchi, T. Sase, M. Inaba, A. Watanabe, N. Akiyama, and F. Murabayashi, "On-chip 500V capacitive isolator for 1 Mbps CAN transceiver," in Proc. Int. CAN Conf., Apr. 2002, pp. 9-15.

- V. R. H. Lorentz, M. M. Wenger, J. L. Grosch, M. Giegerich, M. P. M. Jank, M. März, *et al.*, "Novel cost-efficient contactless distributed monitoring concept for smart battery cells," in Proc. IEEE Int. Symp. Ind. Electron., May 2012, pp. 1342-1347.

- [16] M. Schneider, S. Ilgin, N. Jegenhorst, R. Kube, S. Püttjer, K. R. Riemschneider, et al., "Automotive battery monitoring by wireless cell sensors," in Proc. IEEE Int. Instrum. Meas. Technol. Conf., May 2012, pp. 816-820.

- C.-L. Chen, Y. Hu, W. Luo, C.-Y. Juan, and C.-C. Wang, "A high voltage analog multiplexer with digital calibration for battery management systems," in Proc. IEEE Inter. Conf. IC Des. Technol., May 2012, pp. 1-4.

- [18] C.-L. Chen, D.-S. Wang, J.-J. Li, and C.-C. Wang, "A battery interconnect module with high voltage transceiver using 0.25μm 60V BCD process for battery management systems," in *Proc. Int. SoC Des. Conf.*, Nov. 2012, pp. 1–4.

- [19] A. Danchiv, M. Hulub, and D. Manta, "An area efficient multi-channel high side switch implementation," in *Proc. Eur. Solid-State Circuits Conf.*, Sep. 2011, pp. 327–330.

- [20] J. Kim, E.-H. Chen, J. R. Ren, B. S. Leibowitz, P. Satarzadeh, J. Zerbe, et al., "Equalizer design and performance trade-offs in ADC-based serial links," *IEEE Trans. Circuits Syst.*, vol. 58, no. 9, pp. 2096–2107, Sep. 2011.

- [21] R. Horgervorst, J. P. Tero, G. H. Eschauzier, and J. H. Huijsing, "A compact power-efficient 3 V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries," *IEEE J. Solid-State Circuits*, vol. 29, no. 12, pp. 1505–1513, Dec. 1994.

- [22] R. J. Baker, H. W. Li, and D. E. Boyee, CMOS Circuit Design, Layout, and Simulation, 3rd ed., New York, NY, USA: Wiley, 2010.

- [23] C.-C. Wang, G.-N. Sung, P.-C. Chen, and C.-L. Wey, "A transceiver front end for electronic control units in flexray-based automotive communication systems," *IEEE Trans. Circuits Syst.*, vol. 57, no. 2, pp. 460–470, Jan. 2010.

Chih-Lin Chen (S'10) was born in Taiwan, in 1986. He received the B.S. and M.S. degrees in electrical engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2008 and 2010, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

He is a Visiting Scholar with Brandenburgische Technische Universität, Cottbus, Germany. His current research interests include VLSI design, high voltage mixed-signal circuit design, automobile system design, and sigma-delta ADC design.

**Deng-Shian Wang** was born in Taiwan, in 1988. He received the B.S. and M.S. degrees in electrical engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2011 and 2013, respectively, where he is currently pursuing the Ph.D. degree in electrical engineering.

His current research interests include analog design.

**Jie-Jyun Li** was born in Taiwan, in 1986. He received the B.S. and M.S. degrees in electrical engineering from National Sun Yat-Sen University, Kaohsiung, Taiwan, in 2008 and 2013, respectively.

His current research interests include analog design.

Chua-Chin Wang (M'9–SM'04) received the Ph.D. degree in electrical engineering from the State University of New York at Stony Brook, Stony Brook, NY. USA, in 1992.

He joined the Department of Electrical Engineering, National Sun Yat-Sen University (NSYSU), Kaohsiung, Taiwan, and has been a Full Professor since 1998. He was a Chairman of the Department of Electrical Engineering, NSYSU, from 2009 to 2012. His current research interests include memory and logic circuit design, communication circuit design,

and interfacing I/O circuits. In 2000, he co-founded Asuka Semiconductor Inc., Hsinchu, Taiwan, which is an IC design house, and became an Executive Secretary in 2005. He applies most of his research results on biomedical, memories, consumer electronics, and wireless communication applications, such as implantable ASIC/SoC, DVB-T/H and NTSC TV circuits, low power memory, and high speed digital logic.

Dr. Wang has received the Outstanding Youth Engineer Award of Chinese Engineer Association in 1999 and the NSC Research Award from 1994 to 1999. He has received the Best Inventor Award from NSYSU in 2005, the Distinguished Engineering Professor Award from the Chinese Institute of Engineers and Distinguished Engineer Award from the Chinese Institute of Electrical Engineering in 2006, the Distinguished Electrical Engineering Professor Award from the Chinese Institute of Electrical Engineers in 2007, the Outstanding Paper Award from the 2008 IEEE International Conference of Consumer Electronics in 2008, and the Best Inventor Award in 2009. He was elevated to be Distinguished Professor of NSYSU in 2010. He became an IET Fellow in 2012. He has served as a Program Committee Member in many international conferences. He was a Chair of the IEEE Circuits and Systems Society (CASS), Tainan Chapter, from 2007 to 2008. He was the Founding Chair of the IEEE Solid-State Circuits Society, Tainan Chapter, from 2007 to 2008, and the Founding Consultant of the IEEE NSYSU Student Branch. He is a member of the IEEE CASS Multimedia Systems and Applications, VLSI Systems and Applications, Nanoelectronics and Giga-Scale Systems, and Biomedical Circuits and Systems Technical Committees. He was a Chair of the IEEE CASS Nanoelectronics and Giga-Scale Systems Technical Committee from 2008 to 2009. Since 2010, he has been an Associate Editor for the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—PART I: REGULAR PAPERS and the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS-PART II: EXPRESS BRIEFS. He is currently serving as an Associate Editor for the IEICE Transactions on Electronics and the Journal of Signal Processing. He was a General Chair of the 2007 VLSI/CAD Symposium. He was a General Co-Chair of the 2010 IEEE International Symposium on Next-Generation Electronics. He is a General Chair of the 2011 IEEE International Conference on IC Design and Technology and the 2012 IEEE Asia-Pacific Conference on Circuits and Systems.