# 0.9 V to 5 V Bidirectional Mixed-Voltage I/O Buffer with an ESD Protection Output Stage

Chua-Chin Wang<sup>†</sup>, Senior Member, IEEE, Ron-Chi Kuo, and Jen-Wei Liu

Abstract—A 0.9 V to 5 V (0.9/1.2/1.8/2.5/3.3/5 V) mixed-voltage I/O buffer with NMOS clamping technique is proposed. By using a dynamic gate bias generator to provide appropriate gate drive voltages for the output stage, the I/O buffer can transmit sub- $3 \times VDD$  voltage level signal without gate-oxide overstress hazard. Besides, the leakage current is eliminated by adopting a floating N-well circuit. The maximum data rate are all measured to 66 MHz for 5/3.3/2.5/1.8/1.2/0.9 V with an equivalent probe capacitive load of 10 pF.

Index Terms—mixed-voltage-tolerant, I/O buffer, floating N-well circuit, gate-oxide reliability

#### I. INTRODUCTION

**7** ITH the fast development of CMOS technology, the supply voltage of integrated circuits (IC) is drastically scaled down to reduce power consumption [1]. When chips using different processes and supply voltages are integrated in a PCB-based system, such as in a PCI interface, conventional I/O buffers are not adequate to communicate due to the problems of gate-oxide reliability, hot carrier degradation, and the undesired leakage current path [2]. In past years, many mixed-voltage I/O buffers were reported to deal with the chip interface problems of different voltage levels [1]-[4], [6]. However, most of them can only transmit and receive the signal with the voltage from VDD to  $2 \times VDD$  [1]-[4]. The compatibility with more advanced processes has been ignored. Therefore, a wide range I/O buffer able to simultaneously transmit and receive signal from  $\frac{1}{2} \times VDD$  to sub-3×VDD is deemed as a total solution for these scenarios. To communicate the signal at sub- $3 \times VDD$ , triple stacked transistors are used in the output stage to avoid the gate-oxide overstress. Notably, traditional gate-tracking circuit and floating N-well circuit can not be used directly due to the high voltage signal which is very close to 3×VDD [2], [4]. A protection voltage equal to VDDH-VDD (3.2 V) is required to ensure the gate-oxide reliability. The NMOS clamping technique without any power-consuming DC current path is employed to generate this protection voltage. Besides, the current drive capability with ESD protection is also proposed in this work.

## II. 0.9 V TO 5 V MIXED-VOLTAGE I/O BUFFER

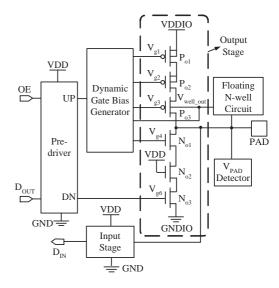

Fig. 1 shows the block diagram of the proposed I/O buffer consisting a Pre-driver, an Input stage, an Output Stage, a Dynamic Gate Bias Generator, a Floating N-well Circuit, and a  $V_{\rm PAD}$  Detector.

C.-C. Wang, R.-C. Kuo, and J.-W. Liu are with the Department of Electrical Engineering, National Sun Yat-Sen University, Kaohsiung, Taiwan (phone: +886-7-525-2000 ext.4144; fax: +886-7-525-4199; e-mail: ccwang@ee.nsysu.edu.tw).

<sup>†</sup>the contact author.

Fig. 1. Block diagram of the proposed mixed-voltage I/O buffer.

## A. Output Stage

Since the supply voltage (VDD) of the core circuits is 1.8 V in 0.18  $\mu$ m CMOS process, the output stage must be realized with three stacked PMOS and NMOS transistors, respectively, for 2×VDD<5 V<3×VDD, as depicted in Fig. 1. Besides, appropriate gate voltages are needed for P<sub>01</sub>~P<sub>03</sub> and N<sub>01</sub>~N<sub>03</sub> to ensure the gate-oxide reliability and correct functions. The detailed operation of output stage is tabulated in Table I.

## B. Pre-driver

The Pre-driver is a simple logic circuit to decode and predrive. When the voltage of control signal OE is at 1.8 V, the I/O buffer operates in the transmitting (TX) mode. The logic state of  $V_{PAD}$  is determined by  $D_{OUT}$ . On the other hand, when the I/O buffer is in the receiving (RX) mode, OE is 0 V.

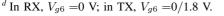

#### C. Input Stage

As shown in Fig. 2, MN604 and MN605 are added to prevent MP602 and MN601 from gate-oxide overstress. MP605 is used to clamp  $V_{i1}$  at 1.8 V when logic 1 is received. MP601 and MN602 are turned off as well as MP604 is turned on to reduce power dissipation in the TX mode.

#### D. Dynamic Gate Bias Generator

The dynamic gate bias generator is composed of a VDDIO Detector,  $V_{g1}$ ,  $V_{g2}$ ,  $V_{g3}$ , and  $V_{g4}$  generators. The details of each subcircuit will be analyzed in the following text.

TABLE I Gate Voltages of the Output Stage

|    | -            |                        | -                      |                          | -                      |

|----|--------------|------------------------|------------------------|--------------------------|------------------------|

|    | VDDIO<br>(V) | V <sub>g1</sub><br>(V) | V <sub>g2</sub><br>(V) | V <sub>g3</sub><br>(V)   | V <sub>g4</sub><br>(V) |

|    | 5            | 5                      | >3.2                   | $1.8/V_{PAD}^{a}$        | $1.8/V_{PAD}^{b}$      |

| RX | 3.3          | 3.3                    | 3.3                    | $1.8/V_{PAD}^{a}$        | $1.8/V_{PAD}^{b}$      |

|    | 2.5          | 2.5                    | 2.5                    | $1.8/V_{PAD}^{a}$        | $1.8/V_{PAD}^{k}$      |

|    | 1.8          | 1.8                    | 1.8                    | $1.8/V_{PAD}^{a}$        | $1.8/V_{PAD}^{b}$      |

|    | 1.2          | 1.2                    | 1.8                    | $1.8/V_{PAD}^{a}$        | $1.8/V_{PAD}^{b}$      |

|    | 0.9          | 0.9                    | 1.8                    | $1.8/\mathrm{V_{PAD}}^a$ | $1.8/V_{PAD}^{b}$      |

| TX | 5            | >3.2/5                 | >3.2                   | >3.2/1.8                 | >3.2/1.8               |

|    | 3.3          | >1.5/3.3               | >1.5                   | >1.5                     | 1.8                    |

|    | 2.5          | >0.7/2.5               | >0.7                   | >0.7                     | 1.8                    |

|    | 1.8          | 0/1.8                  | 0                      | 0                        | 1.8                    |

|    | 1.2          | 0/1.2                  | 0                      | 0                        | 1.8                    |

|    | 0.9          | 0/0.9                  | 0                      | 0                        | 1.8                    |

|    |              |                        |                        |                          |                        |

<sup>*a*</sup> Only when  $V_{PAD} = 5$  V,  $V_{g3} = V_{PAD}$ .

<sup>b</sup> Only when  $V_{PAD} = 5 \text{ V}, V_{g4} > 3.2 \text{ V}.$

<sup>c</sup> In RX or TX,  $V_{well\_out} = 1.8/V_{PAD}$ , and  $V_{g5} = 1.8$  V

Fig. 2. Input stage circuit.

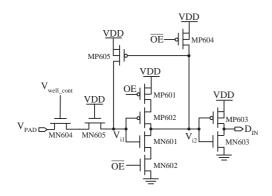

1) Bias Circuit and  $V_{PAD}$  Detector: Referring to Fig. 3, the bias circuit and  $V_{PAD}$  Detector are both realized with a string of diode-connected PMOS transistors. The summation of the threshold voltages of the PMOS must be larger than VDDIO and  $V_{PAD}$ , respectively, such that the transistors would be operated in the sub-threshold region to reduce the static current.

2) VDDIO Detector: VDDIO Detector is implemented with a string of diode-connected PMOS transistors, four detection circuits, (TR0, TR1, TR2, and TR3), and a thermometer code to one-hot code decoder, as illustrated in Fig. 3. As mentioned previously, the summation of the threshold voltages are larger than VDDIO such that the DC current in the PMOS string is very small. The DC voltages VX1~VX11 generated by the PMOS string devices are all proportional to VDDIO. VX4, VX5, VX7, VX8, VX10 are fed into TR0~TR3 for VDDIO detection. Since VX4 and VX5 would be larger than 1.8 V for VDDIO at VDDH, a protection transistor NMOS should be inserted at the gate of PMOS in TR0 and TR1. Through simple glue logic gates, the thermometer code VD0~VD3 could be easily converted into the one-hot code VD50, VD33, VD25, and VD18. The thermometer code VD0~VD3 can be obtained according to various VDDIOs.

Fig. 3. Bias circuit, VDDIO Detector and  $\mathrm{V}_{\mathrm{PAD}}$  Detector.

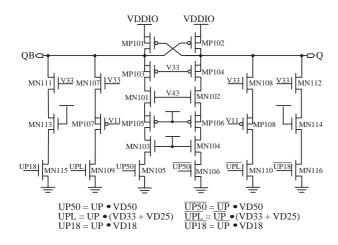

3)  $V_{q1}$  Generator: In Fig. 4,  $V_{q1}$  generator comprises a cross-coupled latch and a voltage level converter, which outputs a pair of opposite signals, Q and QB. It is basically composed of two cross-coupled transistors PMOS with two NMOS transistors in series as discharging paths.  $V_{a1}$  generator contains three pairs of discharging paths which are respectively controlled by the signals UP50, UPL, UP18, and their complementary signals. When VDDIO is fed with 5 V and MN105 is turned on, QB is discharged to 3.3 V through the first pair of discharging paths (MP103, MN101, MP105, MN103, and MN105) while Q is pulled up to VDDIO. When VDDIO is fed with 3.3/2.5 V, the second pair of discharging paths (MN107~MN110, MP107, and MP108) is activated, which is controlled by UPL and  $\overline{UPL}$ . When VDDIO is fed with 1.8/1.2/0.9 V, the third discharging path (MN111~MN116) is on. Referring to the logic equations in Fig. 4, any input voltage will appear in only one pair of discharging paths.

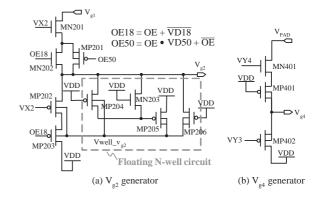

4)  $V_{g2}$  and  $V_{g4}$  Generator: Fig. 5 (a) shows the schematic of  $V_{g2}$  generator. MN201 is a clamping NMOS, which can only pass the signal smaller than VX2–V<sub>thn</sub>, where V<sub>thn</sub> is the threshold voltage of NMOS. When VDDIO is 5 V, OE18 and OE50 are both biased at 1.8 V such that  $V_{g2}$  can be biased at 3.2 V (VX2-V<sub>thn</sub>) through MN202 and MP201 without gate-oxide overstress. MP202 is turned off provided that VX2 is higher than 3.2 V. If VDDIO is lower than 1.8 V such that MN202 and MP201 are turned off.  $V_{g2}$  can be operated at 1.8 V through MP203 and MP203, when VX2 is lower than 1.8 V. Besides, the undesired leakage current caused by the parasitic diodes of MP202 and MP203 can be eliminated by connecting their N-well to a floating N-well circuit comprising MN203, MP204, and MP206.

$V_{g4}$  generator is shown in Fig. 5 (b). It pulls  $V_{g4}$  to 3.2 V when  $V_{PAD}$  is 5 V and keeps  $V_{g4}$  at 1.8 V for  $V_{PAD} = 3.3$  V. When  $V_{PAD}$  is 5 V,  $V_{g4}$  is biased at 3.2 V (VY4 –  $V_{thn}$ ) by the clamping NMOS MN401. When  $V_{PAD}$  is biased at 3.3/2.5/1.8/1.2/0.9/0 V, VY4 -  $V_{thn}$  is smaller than 1.8 V and blocked by MP401.  $V_{g4}$  is then biased at 1.8 V by MP402,

Fig. 4.  $V_{g1}$  generator.

because VY3 is lower than 1.8 V.

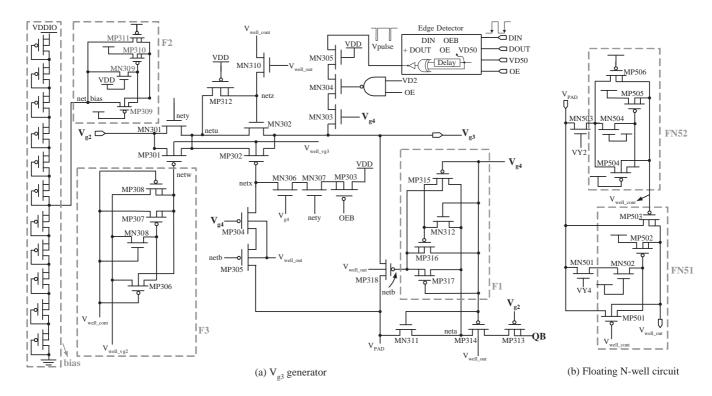

5)  $V_{g3}$  Generator: The proposed  $V_{g3}$  generator is depicted in Fig. 6 (a). It can be observed that both  $V_{PAD}$  and  $V_{g2}$  are fed into  $V_{g3}$  generator. By detecting two signals, VDDIO and OE, a corresponding  $V_{g3}$  will be generated. To reduce the power consumption,  $V_{g3}$  generator combines the voltage-generating function with the gate-tracking capability in this work. In the receiving mode, when VDDIO is fed with 1.8/1.2/0.9 V and  $V_{PAD}$  is biased at 5 V, the voltage of  $V_{neta}$  and  $V_{netb}$  are clamped at 3.2 V for passing  $V_{PAD}$  to  $V_{g3}$  to avoid the leakage current problem. Besides, MN301 is turned off by floating Nwell circuit  $F_2$  when the voltage of  $V_{net bias}$  is lower than 1.8V. When  $V_{PAD}$  is 0 V, an Edge Detector is adopted to prevent transistor  $P_{o3}$  from gate-oxide overstress. When  $V_{PAD}$  is at 2.5/3.3 V, Vnetb is generated at 1.8 V by floating N-well circuit F1. Then,  $V_{PAD}$  is passed to MP318 to turn off the output stage  $P_{0,3}$ . In the transmitting mode, when VDDIO is operated at 5 V, a negative pulse, which is triggered at the negative edge of  $D_{OUT}$ , would pulled  $V_{g3}$  down to 1.8 V. Thus, the gateoxide overstress can be avoided. When VDDIO is operated at 1.8/1.2/0.9 V,  $V_{q2}$  is biased at 1.8/1.2/0.9 V and MN304 is turned off to protect  $V_{g3}$  from any leakage current.

## E. Floating N-well Circuit

To avoid the undesired leakage current path through the parasitic diode of  $P_{o3}$ ,  $V_{well\_out}$  is varied with different  $V_{PAD}$  by the floating N-well circuit. The proposed floating N-well circuit is composed of two traditional floating N-well cells, FN51 and FN52, as shown in Fig. 6 (b). With the clamping NMOS MN503, FN52 can output the signal  $V_{well\_cont}$  at max(VY2– $V_{thn}$ , 1.8 V). When  $V_{PAD}$  is operated at 3.3 V,  $V_{well\_cont}$  is biased at 1.8 V. When  $V_{PAD}$  is 5 V,  $V_{well\_cont}$  at 3.2 V (= VY2 -  $V_{thn}$ ) is used as the protection voltage for MP503. On the other hand, FN51 can generate the output signal  $V_{well\_out} = \max(V_{PAD}, V_{well\_cont})$ .

## F. ESD Protection Consideration

In traditional I/O buffers, the parasitic diode of the PMOS in the output stage can provide a discharge path for the ESD current. However, the parasitic diode connected to the I/O PAD

Fig. 5.  $V_{g2}$  generator and  $V_{g4}$  generator.

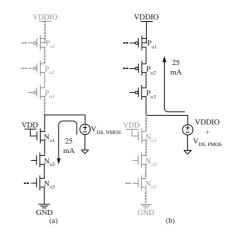

and VDDIO does not exist due to the floating n-well circuit in the mixed-voltage-tolerant I/O buffer. Thus, the ESD capability of the mixed-voltage-tolerant I/O buffer is worse than that of traditional I/O buffers given the same size. In order to retain enough ESD capability, the penalty is the large area of NMOS and PMOS in Output stage. From the measurement results of several previous works [1]-[4], the ESD strength of the stacked output stage with their current driving ability higher than 25 mA can be equalized to 2 kV for HBM (human body model) and 200 V for MM (machine model) [5], [6]. Fig. 7 shows the simplified circuit with ESD consideration through discharging path and charging path.  $V_{DS,NMOS}$  and  $V_{DS,PMOS}$  can be derived as follows,

$$V_{\rm DS,PMOS} = \frac{V_{\rm IL} - V_{\rm SS}}{2} \tag{1}$$

$$V_{\rm DS,NMOS} = \frac{V_{\rm IH} - V_{\rm SS}}{2} \tag{2}$$

where  $V_{IL}$  and  $V_{IH}$  are set to  $0.35 \times VDD$  and  $0.65 \times VDD$ , respectively [5]. Moreover, Output Stage are operated in the triode region. Thus, by taking above conditions and the characteristic of transistors in triode region into consideration, the W/L ratio of PMOS and NMOS in the Output Stage can be determined to be 720  $\mu$ m/ 180 nm and 180  $\mu$ m/ 180 nm, respectively.

#### **III. MEASUREMENT RESULTS**

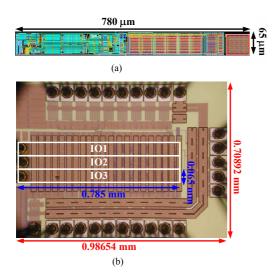

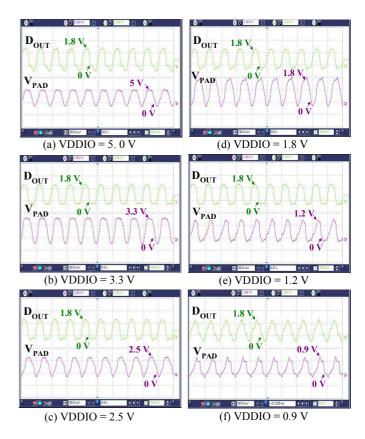

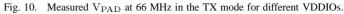

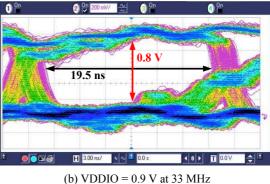

The proposed design is implemented with a typical 0.18  $\mu$ m logic CMOS process. Fig. 8 shows the layout and the die photo of the proposed mixed-voltage I/O buffer. Fig. 9 depicts the waveforms of  $V_{\rm PAD}$  and  $D_{\rm IN}$  with different  $V_{\rm PAD}$  voltages in the RX mode, whereas  $\mathrm{D}_\mathrm{IN}$  is recovered at 1.8 V in all cases. The maximum TX data rate with different VDDIOs is measured, as shown in Fig. 10. The mark level of  $V_{\rm PAD}$ is same as the voltage level of VDDIO. Fig. 11 reveals the measured eye diagram of the output signal in the TX mode when VDDIO=5.0 V at 40 MHz and VDDIO=0.9 V at 33 MHz, respectively. The sampling windows are all higher than 18 ns for both TX/RX modes. The performance of the proposed mixed-voltage I/O buffer is summarized in Table II compared with several previous I/O buffers. Table II shows that a wide voltage range, sub-3×VDD, is successfully achieved by this work.

TABLE II

PERFORMANCE CAPARISON OF MIXED-VOLTAGE I/O BUFFER

|           | Year | Transmitting voltage mode<br>(V) | Process (µm) | Frequency<br>(MHz) | Area<br>(µm×µm) |

|-----------|------|----------------------------------|--------------|--------------------|-----------------|

| This work | 2009 | 0.9/1.2/1.8/2.5/3.5/5            | 0.18         | 66                 | 65×785          |

| [6]       | 2009 | 5/3.3/1.8                        | 0.35         | 60                 | 1328×1126       |

| [1]       | 2008 | 1.5/3.3                          | 0.18         | 266                | N/A             |

| [2]       | 2007 | 1.2/2.5                          | 0.13         | 133                | 107.73×65.38    |

| [3]       | 2007 | 1.8/3.3                          | 0.18         | 200                | N/A             |

| [4]       | 2006 | 2.5/5                            | 0.25         | 50                 | N/A             |

Fig. 6.  $V_{g3}$  generator circuit and the floating N-well circuit.

## IV. CONCLUSION

A 0.9 V to 5 V mixed-voltage tolerant I/O buffer is proposed in this paper. The signal from  $\frac{1}{2} \times VDD$  to sub-3×VDD can be transmitted and received simultaneously. Besides, the effects of gate-oxide overstress and the leakage current are both eliminated.

## V. ACKNOWLEDGMENT

This investigation is partially supported by Ministry of Economic Affairs, Taiwan, under grant 98-EC-17-A-01-S1-104, under grant 98-EC-17-A-02-S2-0017, under grant 98-EC-17-A-07-S2-0010, and under grant 98-EC-17-A-01-S1-133. It is also partially supported by National Science Council, Taiwan, under grant NSC98-2220-E-110-009, and partially supported by National Health Research Institutes under grant NHRI-EX99-9732EI. The authors would like to express their deepest gratefulness to CIC (Chip Implementation Center) of NARL (National Applied Research Laboratories), Taiwan, for their thoughtful chip fabrication service.

Fig. 7. The simplified circuit of output stage with ESD protection. (a) Discharging path. (b) Charging path.

## References

M.-D. Ker, T.-M. Wang, and F.-L. Hu, "Design on mixed-voltage I/O buffers with slew-rate control in low-voltage CMOS process," in the *Proc.* of 15th Int. Conf. on Electronics, Circuits and Systems, pp. 1047-1050, Aug. 2008.

- [2] H.-W. Tsai and M.-D. Ker, "Design of 2×VDD-tolerant I/O buffer with considerations of gate-oxide reliability and hot-carrier degradation," in the *Proc. of 14th Int. Conf. on Electronics, Circuits and Systems*, vol. 4, pp. 1240-1243, Dec. 2007.

- [3] G. Liu, Y. Wang, and S. Jia, "A new design of mixed-voltage I/O buffers with low-voltage-thin-oxide CMOS process," in the *Proc. of 7th Int. Conf.* on ASIC, pp.201-204, Oct. 2007.

- [4] M.-D. Ker, S.-L. Chen, and C.-S. Tsai, "Overview and design of mixedvoltage I/O buffers with low-voltage thin-oxide CMOS transistors," *IEEE Tran. on Circuits and Systems I: Regular Papers*, vol. 53, no. 2, pp. 1934-1945, Sep. 2006.

- [5] JEDEC Standard, JESD82-7A, Oct. 2004.

- [6] T.-J. Lee, T.-Y. Chang, and C.-C. Wang, "Wide-range 5.0/3.3/1.8 V I/O buffer using 0.35-um 3.3-V CMOS technology," *IEEE Trans. on Circuits* and Systems-I: Regular Papers, vol. 36, No. 4, pp. 763-772, Apr. 2009.

Fig. 8. (a) Layout (b) Die photo of the proposed mixed-voltage I/O buffer.

Fig. 9. Measured  $\mathrm{D}_{\mathrm{IN}}$  in the RX mode for different  $\mathrm{V}_{\mathrm{PAD}}$  voltages.

Fig. 11. Measured eye diagrams of the output signal  $V_{\rm PAD}$  (a) when VDDIO = 5.0 V at 40 MHz (b) when VDDIO = 0.9 V at 33 MHz.