# A linear LDO regulator with modified NMCF frequency compensation independent of off-chip capacitor and ESR

Chua-Chin Wang · Chi-Chun Huang · U. Fat Chio

Received: 1 February 2007/Revised: 28 September 2009/Accepted: 28 September 2009/Published online: 11 October 2009 © Springer Science+Business Media, LLC 2009

**Abstract** This paper presents a novel compensation design for regulators, i.e., modified NMCF (nested Miller compensation with feedforward Gm stage), resulting in a linear LDO (low dropout) regulator whose performance is independent of the off-chip capacitor and its ESR (equivalent series resistor). The proposed compensation method ensures the stability of the feedback loop and the sufficient phase margin of the LDO regulator. Besides, the transient response become faster. The analysis of the stability is derived to solidify the proposed design. The proposed design is implemented using TSMC 0.35 μm 2P4M CMOS process. The results verify the performance and the stability on silicon. The power supply rejection ratio is 25 dB @ [200 Hz, 3 MHz], [50  $\Omega$ , 500  $\Omega$ ] provided that the input voltage varies from 4 to 5 V.

**Keywords** LDO regulator · Modified NMCF · Frequency compensation · ESR

#### 1 Introduction

The LDO (low-dropout) regulator is generally utilized to translate a voltage level or provide a stable output voltage, which has been considered as one of the important

C.-C. Wang (⋈) · C.-C. Huang · U. F. Chio Department of Electrical Engineering, National Sun Yat-Sen University, 70 Lian-Hai Rd., Kaohsiung, Taiwan

e-mail: ccwang@ee.nsysu.edu.tw

C.-C. Huang

e-mail: rouff@vlsi.ee.nsysu.edu.tw

U. F. Chio

e-mail: vencedor@so-net.net.tw

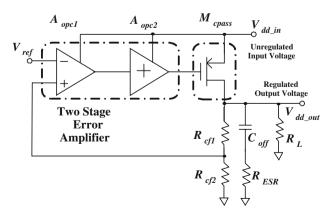

medical chips [3]. Traditional linear LDO regulators usually consist of a two-stage error amplifier, a power output stage and a negative feedback loop. However, since the stability and accuracy of the regulated output voltage is the most critical factor in many field applications such as biomedical chips, traditional designs suffer from poor efficiency as the difference between the input and output voltages is increased [4]. In order to attain a fast transient response and an accurate output voltage, several prior LDO regulators were proposed to use high gain amplifiers with a cascade or cascode technology. It results in the stability problem due to the appearance of inherent three poles. Besides, the varying load current also affects the stability [5, 6]. Thus, a frequency compensation technique to ensure the stability of the LDO regulator was proposed to resolve this problem [5–7]. Otherwise, the circuitry will become unstable due to the inherent three poles if there is no any compensation mechanism. What worse is that the equivalent loading impedance of the LDO regulator might not be a constant. It then leads to the output pole drifting. Thus, the loop stability of the LDO regulator is uncertain. An off-chip capacitor  $C_{\text{off}}$ , as shown in Fig. 1, was proposed to maintain the stability of the LDO regulator in several research works, [4, 8, 9]. The off-chip capacitor and its ESR (equivalent series resistor) are designed to move the zero to achieve a pole-zero cancellation and keep the phase margin larger than zero degree [10]. However, the off-chip capacitor increases the area of printedcircuit board and the value of the ESR might drift owing to the variation of the temperature and different materials [11]. Therefore, the off-chip capacitor scheme is also not deemed as a reliable solution. In this work, a new compensation method independent of the off-chip capacitor and its ESR is

components for the power management of wireless appli-

cations, e.g., cellular phones, hand-held computers, battery charging [1, 2] and particularly implanted wireless bio-

presented to enhance the LDO regulator's performance regarding the transient response and the noise rejection.

## 2 LDO regulator using NMCF

A traditional LDO regulator is shown in Fig. 1, where a bandgap bias circuit generates a PVT(process, supply voltage, temperature)-independent reference voltage  $V_{\rm ref}$ . The series resistors,  $R_{cf1}$ ,  $R_{cf2}$ , monitor the output voltage by a simple voltage division. A feedback voltage  $V_{\rm fb}$  is fed back to be compared with  $V_{ref}$  by the error amplifier. The error amplifier then feeds a control voltage into the pass transistor  $M_{\rm cpass}$  to regulate the output voltage according to the difference between  $V_{\text{ref}}$  and  $V_{\text{fb}}$ . The faster speed of the feedback loop comes along with the more stable output voltage. Therefore, a large gain is required to ensure that the feedback loop stays stable. Hence, the frequency compensation becomes a critical issue in the LDO regulator design. However, there is a trade-off between the loop gain and the bandwidth of the circuit.

#### 2.1 Modified NMCF compensation

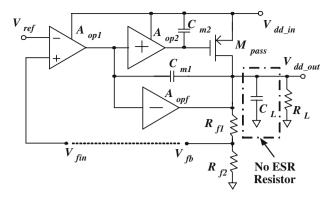

The structure of the proposed LDO regulator is shown in Fig. 2. It is composed of two cascaded error amplifiers,  $A_{\rm op1}, A_{\rm op2}$ , a pass transistor,  $M_{\rm pass}$ , series resistors,  $R_{\rm f1}, R_{\rm f2}$ , two compensation capacitors,  $C_{\rm m1}$ ,  $C_{\rm m2}$ , and a feedforward transconductance amplifier stage,  $A_{opf}$ . What we propose is to insert a feed forward Gm boosting amplifier between the output of the first error amplifier and the resistor-based voltage divider. Meanwhile, two compensation capacitors are added on the source and the drain of the pass element to mimic the Miller capacitor compensation. It is then called the modified NMCF (nested Miller compensation with feedforward Gm stage) design.

In order to simplify the analysis of the frequency compensation, we assume that  $g_{mi}$ ,  $R_{oi}$  are the transconductance

Fig. 1 The classical LDO regulator with the off-chip capacitor

Fig. 2 The structure of the proposed LDO regulator

and the output impedance of the amplifier  $A_{\rm opi}$ , respectively, where i = 1, 2, or f.  $g_{\rm mp}$  and  $R_{\rm op}$  denote the transconductance and the output impedance of the transistor  $M_{\text{pass}}$ , respectively. Besides, we assume that the gain of each amplifier is much larger than the unit gain. The load capacitor,  $C_L$ , and the compensation capacitors are much larger than parasitic capacitors which could be neglected in the analysis.

Based on these assumptions, the open loop transfer function is given by

$$T(s) = \frac{V_{\text{fb}}(s)}{V_{\text{fin}}(s)} = \frac{\text{TDC} \cdot \text{Zero}(s)}{(1 + \frac{s}{p_1})(1 + \frac{s}{p_2})(1 + \frac{s}{p_3})},$$

$$\text{TDC} = (g_{\text{m1}}g_{\text{m2}}g_{\text{mp}}R_{\text{o1}}R_{\text{o2}})\left(\frac{R_{\text{op}}R_L}{R_{\text{op}} + R_L}\right)\left(\frac{R_{f2}}{R_{f1} + R_{f2}}\right),$$

$$p_1 = \frac{R_{\text{op}} + R_L}{C_{\text{m1}}g_{\text{m2}}g_{\text{mp}}R_{\text{o1}}R_{\text{o2}}R_{\text{op}}R_L},$$

$$p_2 = \frac{1}{R_{\text{o2}}C_{\text{m2}}},$$

$$p_3 = \frac{R_{\text{op}} + R_L}{R_{\text{op}}R_LC_L},$$

$$\text{Zero}(s) = 1 + \left(\frac{g_{\text{mf}}C_{\text{m2}}}{g_{\text{m2}}g_{\text{mp}}}\right)s - \left(\frac{C_{\text{m1}}C_{\text{m2}}}{g_{\text{m2}}g_{\text{mp}}}\right)s^2,$$

$$(1)$$

where TDC is the DC loop gain, and  $p_1$  is the dominant Pole. According to Eq. 1, the LHP zero is found be as follows,

$$z_{1} = -\frac{g_{\rm mf}}{2C_{\rm m1}} \left( \sqrt{1 + 4\frac{C_{\rm m1}}{C_{\rm m2}} \frac{g_{\rm m2}g_{\rm mp}}{g_{\rm mf}}} + 1 \right). \tag{2}$$

By contrast, the RHP zero is also derived to be

$$z_2 = \frac{g_{\rm mf}}{2C_{\rm m1}} \left( \sqrt{1 + 4 \frac{C_{\rm m1}}{C_{\rm m2}} \frac{g_{\rm m2}g_{\rm mp}}{g_{\rm mf}}} - 1 \right).$$

(3)

The LHP zero should be located after  $p_2$ ,  $p_3$  for the stability purpose [7]. Thus, the following conditions must be held, given  $C_{\text{m1}} \ll C_{\text{m2}}$ , and  $R_{\text{op}} \ll R_L : g_{\text{mf}} \ge \frac{C_{\text{m1}}}{R_{\text{op}}C_L}$ ,  $g_{\text{mf}} \ge \frac{C_{\text{m1}}}{R_{\text{o2}}C_{\text{m2}}}$ . By setting  $p_2$  and  $p_3$  larger than the required GBW (gain-

bandwidth product), the GBW is then found to be

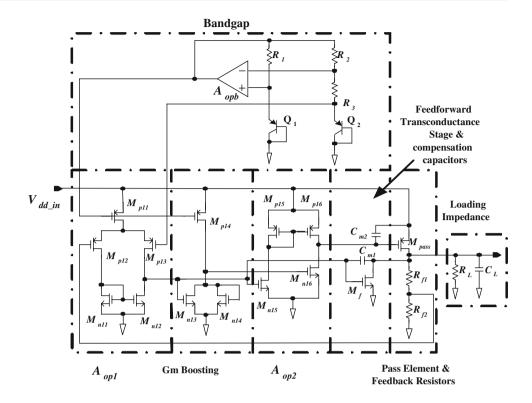

Fig. 3 The schematic of the proposed LDO regulator

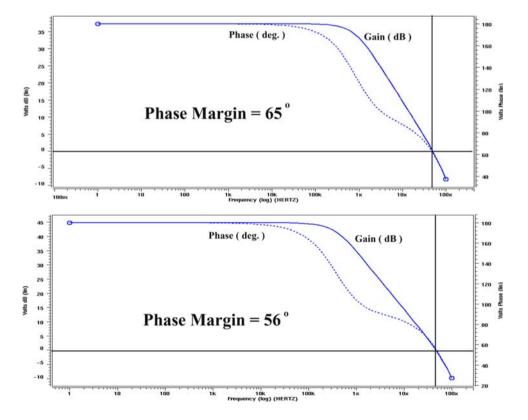

**Fig. 4** Loop gain and loop phase at 0 and 75°C

$$GBW = \frac{g_{m1}}{C_{m1}}.$$

(4)

The phase margin (PM) is also derived to be

$$\begin{split} PM &\approx 90^{\circ} - \tan^{-1}\!\left(\!\frac{GBW}{p_2}\!\right) - tan^{-1}\!\left(\!\frac{GBW}{p_3}\!\right) \\ &- tan^{-1}\!\left(\!\frac{GBW}{z_2}\!\right) + tan^{-1}\!\left(\!\frac{GBW}{|z_1|}\!\right) > 60^{\circ}. \end{split} \tag{5}$$

If the phase margin of a loop greater than  $60^{\circ}$ , the time domain response of this loop will get rid of ringing [12]. In short, a stable LDO regulator independent of the ESR can be attained by tuning  $g_{\rm mf}$ ,  $C_{\rm m1}$  and  $C_{\rm m2}$  despite that the load capacitor  $C_L$  varies.

## 2.2 Circuit design

The schematic of the proposed design is shown in Fig. 3.  $R_1$ ,  $R_2$ ,  $R_3$ ,  $Q_1$ ,  $Q_2$ , and  $A_{\rm opb}$  act as the bandgap bias circuitry. The reference voltage is easily derived as

$$V_{\text{ref}} = V_{\text{EB2}} + \left(1 + \frac{R_2}{R_3}\right) V_t \ln\left(\frac{A_{Q2}}{A_{Q1}}\right),\tag{6}$$

where  $A_{Q1}$  and  $A_{Q2}$  are the emitter area of  $Q_1$  and  $Q_2$ , respectively.  $M_{\rm p11}-M_{\rm p13},\,M_{\rm n11},\,$  and  $M_{\rm n12}$  constitute the first stage of the error amplifier,  $A_{\rm op1},\,$  while  $M_{\rm p15},\,$   $M_{\rm p16},\,M_{\rm n15},\,$  and  $M_{\rm n16}$  construct the second stage,  $A_{\rm op2}.\,$   $R_{\rm f1}$  and  $R_{\rm f2}$  are the feedback series resistors.  $C_{\rm m1}$  and  $C_{\rm m2}$  are the compensation capacitors.  $M_f$  is the feedforward transconductance stage, i.e.,  $A_{\rm opf},\,$  which generates a negative small signal to cancel the feedforward current passing through  $C_{\rm m1}$  at high frequency.  $M_{\rm p14},M_{\rm n13},\,$  and  $M_{\rm n14}$  are in charge of gmboosting for the loop.

The pass transistor plays a critical role in the design of the LDO regulator. There are five types of pass transistors made up with different transistors to be chosen: Darlington pairs, NPN, PNP, NMOS, and PMOS. The first three components are bipolar junction transistors which could provide a large output current, but produce larger power consumption. Additionally, the dropout voltage is another important factor when it comes to the selection of the pass transistor. Since NMOS needs its gate voltage higher than its source voltage to get into the saturation region, the dropout voltage is high if it is used as the pass transistor. Therefore, PMOS is selected in the proposed design.

#### 3 Simulation and implementation

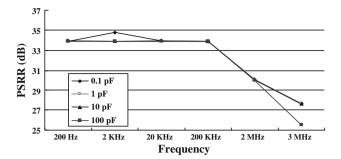

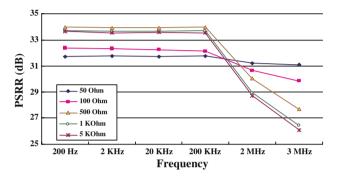

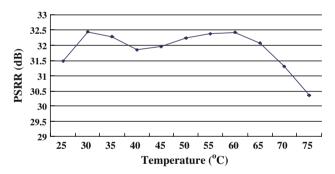

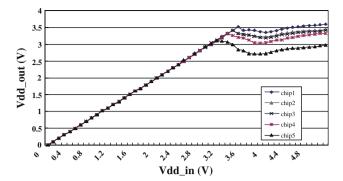

We select the value of  $C_{\rm m1}$  and  $C_{\rm m2}$  to be equal to 0.1 and 30 pF, respectively, basing on the analysis of Eqs. 1–5. Figure 4 shows that the proposed design is stable in the temperature range [0, 75°C]. The PSRR (power supply rejection ratio) results given different  $C_L$  and  $R_L$  are shown in Figs. 5 and 6, respectively. Figure 7 shows the overall

**Fig. 5** PSRR of the proposed LDO regulator at different CL (RL = 100)

Fig. 6 PSRR of the proposed LDO regulator at different RL (CL = 10~pF)

Fig. 7 PSRR of the proposed LDO regulator at [25, 75°C] (RL = 100, CL = 10 pF)

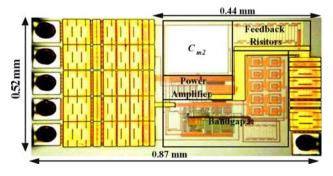

Fig. 8 Die photo of the proposed LDO Regulator

Fig. 9 Output voltage versus input voltage at different chips

Table 1 Performance comparison of LDO regulators

|                              | [4]                  | [8]                        | Ours                     |

|------------------------------|----------------------|----------------------------|--------------------------|

| PSRR (dB)                    | 54                   | 38                         | 25                       |

| CMOS process (µm)            | 0.25                 | 0.5                        | 0.35                     |

| Chip area (mm <sup>2</sup> ) | 0.21                 | 1                          | 0.45                     |

| Max. freq.                   | N/A                  | 3 KHz                      | 3 MHz                    |

| Max. O/P power (mW)          | 720                  | 990                        | 360                      |

| $V_{\rm dd\_in}$ ripple      | N/A                  | N/A                        | 1 V                      |

| Dropout voltage (V)          | 0.5                  | 0.3                        | 0.3                      |

| $C_{ m off-chip}$ needed     | Yes                  | Yes                        | No                       |

| Applications                 | Battery-<br>operated | DC-voltage-<br>transferred | RF-power-<br>transferred |

PSRR given different temperatures. In short, the PSRR is 25 dB @ [200 Hz, 3 MHz], [50  $\Omega$ , } 500  $\Omega$ ] provided that the input voltage varies from 4 to 5 V.

TSMC (Taiwan Semiconductor Manufacturing Company) 0.35  $\mu$ m 2P4M CMOS process is adopted to carry out the proposed design. The die photo of the proposed LDO regulator is shown in Fig. 8 and the chip area is 870  $\mu$ m  $\times$  520  $\mu$ m. Figure 9 shows the regulated output voltage  $V_{\rm dd\_out}$  versus the input voltage  $V_{\rm dd\_in}$  in different chips. Referring to Fig. 9, all  $V_{\rm dd\_out}$  value of these chips varies from 3.0 to 3.6V given  $V_{\rm dd\_in}$  from 3.7 to 5.2 V except chip 5. It is good enough to be used in RF-power-transferred applications, e.g., RFID, wireless no battery implantable biomedical chips.

A performance comparison of the proposed design with several prior LDOs is summarized in Table 1. Our design provides the least dropout voltage, the maximum operation frequency without using any off-chip capacitor.

## 4 Conclusion

We have proposed a LDO regulator with a modified NMCF compensation design. Its outstanding performance is

independent of the off-chip capacitor and its ESR. The detailed compensation analysis of the proposed design is also revealed to illustrate the methodology. The simulation and measurement results justify that the supply ripple rejection is independent of the load resistor in the range from  $50~\Omega$  to  $500\Omega$ . Moreover, the PSRR keeps 25 dB even if the operating frequency is up to 3 MHz.

Acknowledgments This research was partially supported by National Science Council under grant NSC96-2628-E-110-019, NSC96-2923-E-110-001, and NHRI EX98-9732EI. Furthermore, the authors would like to express their deepest gratefulness to CIC (Chip Implementation Center) of NAPL (National Applied Research Laboratories), Taiwan, for their thoughtful chip fabrication service. The authors also like to thank "Aim for Top University Plan" project of NSYSU and Ministry of Education, Taiwan, for partially supporting the research.

#### References

- 1. Benardon, D., & Muellauer, M. (2001). A high-precision low-drop linear regulator for battery charging application. In *IEEE* solid-state circuits conference, 2001. ESSCIRC 2001. Proceedings of the 27th European (pp. 65–68), Sep. 2001.

- Tsai, C.-C., Lin, C.-Y., Hwang, Y.-S., Lee, W.-T., & Lee, T.-Y. (2004). A multi-mode LDO-based Li-ion battery charger in 0.35 uM CMOS technology. In 2004 Asian-Pacific conference on circuits and systems (pp. 49–52), Dec. 2004.

- Akin, T., Najafi, K., & Bradley, R. M. (1998). A wireless implantable multichannel digital neural recording system for a micromachined sieve electrode. *IEEE Journal of Solid-State Circuits*, 33(1), 109–118.

- Barber, T. J. Jr., Ho, S., & Ferguson, P. Jr. (2002). Multi-mode CMOS low dropout voltage regulator for GSM handsets. In Symposium on VLSI circuits digest of technical papers (pp. 284-287), June 2002.

- Kwok, K. C., & Mok, P. K. T. (2002). Pole-zero tracking frequency compensation for low dropout regulator. In 2002 IEEE international symposium on circuits and systems (ISCAS'02) (Vol. 4, pp. 735–738).

- Leung, K. N., Mok, P. K. T., & Ki, W. H. (1998). A novel frequency compensation technique for low-voltage low-dropout regulator. In 1999 International symposium on circuits and systems (ISCAS'98) (Vol. 5, 102–105).

- Leung, K. N., & Mok, P. K. T. (2001). Analysis of multistage amplifier-frequency compensation. *IEEE Transactions on Cir*cuits and Systems, 8(9), 1041–1056.

- den Besten, G. W., & Nauta, B. (1998). Embedded 5 V-to-3.3 V voltage regulator for supplying digital IC's in 3.3 V CMOS technology. *IEEE Journal of Solid-State Circuits*, 33(7), 956–962.

- Stanescu, C. (2003). Buffer stage foe fast response LDO. 2003 International Semiconductor Conference, 2, 357–360.

- Chava, C. K., & Martinez, J. S. (2004). A frequency compensation scheme for LDO voltage regulators. *IEEE Transactions on Circuits and Systems*, 51(6), 1041–1051.

- Lu, S.-H., Huang, W.-J., & Liu, S.-I. (2005). A fast-recovery low dropout linear regulator for any-type output capacitors. In 2005 Asian solid-state circuits conference (pp. 497–500), Nov. 2005.

- Allen, P. E., & Holberg, D. R. (2002). CMOS analog circuit design. New York: Oxford.

Chua-Chin Wang was born in Taiwan in 1962. He received the B.S. degree in electrical engineering from National Taiwan University in 1984, and the M.S. and Ph.D. degree in Electrical Engineering from State University of New York in Stony Brook in 1988 and 1992, respectively. In 1992 he joined Department of Electrical Engineering, National Sun Yat-Sen University, Taiwan. He is currently a professor. His recent research interests include VLSI

design, low-power and high-speed logic circuit design, neural networks, and wireless communication. He is also a senior member of IEEE.

Chi-Chun Huang was born in Taiwan in 1980. He received the B.S. degree in Department of Electrical Engineering in National Cheng Kung University in 2003 and the M.S. in Department of Electrical Engineering in National Sun Yat-Sen University in 2005. He is currently working toward the Ph.D. in the Department of Electrical Engineering National Sun Yat-Sen University, Kaohsiung, Taiwan. His recent research interests include VLS design,

mixed signal circuits, and biomedical signal processing.

U. Fat Chio was born in 1979. He received the B.S. degree and the M.S. in Department of Engineering Electrical National Sun Yat-Sen University in 2002 and 2004. He is currently working toward the Ph.D. in the Department of Electrical Engineering University of Macau, China. His research interests include VLSI design, mixed signal circuits, and biomedical processing.