# High-PSR sync separator for TV signals

Chua-Chin Wang · Chia-Hao Hsu · Chi-Chun Huang · Tzung-Je Lee · Chien-Chih Hung · Ya-Hsin Hsueh · Ron Hu

Received: 1 November 2006/Revised: 5 December 2008/Accepted: 2 March 2009/Published online: 19 March 2009 © Springer Science+Business Media, LLC 2009

**Abstract** This paper presents a novel NTSC video sync separator (NSS) with a high-PSR (power supply rejection) bias generation circuitry (BGC) which comprises a temperature compensation circuitry. The proposed BGC utilizes step-down regulators and a bandgap-based bias with cascode current control. The clamping voltages required for sync separation from an NTSC signal are generated. Detailed PSR analysis of the proposed BGC is also derived to circumscribe the clamping voltage variation. The proposed design is carried out using 0.35 µm 2P4M CMOS process. The measurement results verify that the HSYNC, the composite signal, and the Line 21 caption data can be separated successfully even if a 1 V noise is coupled in the supply voltage. The measured power consumption of the proposed chip is 31.92 mW.

**Keywords** NTSC · TV · Wireless network · Line 21 · **PSR**

#### 1 Introduction

Video decoders for NTSC TV products, e.g., [6], heavily rely on precise clock sources, particularly HSYNC, VSYNC, color burst, even/odd field, and back porch [3], [5]. However, these clock sources built in the TV-related products, particularly the compact hand-held or mobile TVs, will be drastically affected by the ambient temperature as well as the highly unreliable power supplies. Those mentioned clock signals existing in the NTSC composite signals might not be extracted correctly. On top of that, the generated heat will be very likely to drift the clock edges if there is no compensation mechanism. Severe damages are possibly made, e.g., fuzzy image and ghost shadow problems. Lots of work have been done to develop design methods of the NTSC sync separation circuitry. Most of the product datasheets, e.g., [5], were focused on the functionality of video signal processing. On the other hand, most of the related prior works were focused on either the bandgap designs [1, 4], or simple clock generations [6, 9, 10]. A fact which has been long ignored is that the hostile environment jeopardizes the clock locking and the voltage clamping of a video decoder [11]. Besides, the peak-topeak amplitude of the received NTSC signals, called  $V_{nn}$ , will vary drastically. A temperature-insensitive bias generation circuitry, thus, is required to provide stable reference voltages for clock tracking, data slicing, and noise rejection. Hence, we present an NTSC sync separator

C.-C. Wang ( ) · C.-H. Hsu · C.-C. Huang · T.-J. Lee · C.-C. Hung

Department of Electrical Engineering, National Sun Yat-Sen University, 70 Lian-Hai Rd., Kaohsiung, Taiwan

e-mail: ccwang@ee.nsysu.edu.tw

C.-H. Hsu

e-mail: chhsu@vlsi.ee.nsysu.edu.tw

C.-C. Huang

e-mail: rouff@vlsi.ee.nsysu.edu.tw

e-mail: waller@vlsi.ee.nsysu.edu.tw

C.-C. Hung

e-mail: goi@vlsi.ee.nsysu.edu.tw

Y -H Hsueh

Department of Electronic Engineering, National Yunlin University of Science and Technology, Yunlin, Taiwan

e-mail: hsuehyh@yuntech.edu.tw

R. Hu

Asuka Semiconductor Inc., Hsinchu, Taiwan

e-mail: ron@asuka-semi.com.tw

with a robust temperature-insensitive bias with high PSR (power supply rejection) comprising regulators and a reference voltage generator to resolve the mentioned problems. Moreover, a system clock is also generated for the following DSP (digital signal processing) core. The caption data carried in the Line 21 of the NTSC signal is also separated by the proposed design.

# 2 Robust NSTC sync separator

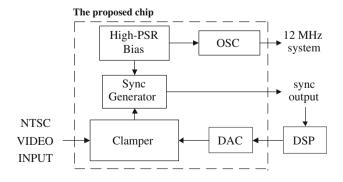

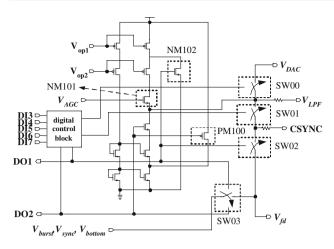

Although Electronic Industries Alliance (EIA) has announced that the  $V_{pp}$  of the NTSC signal is set to 140 IREs [3], the amplitude of  $V_{pp}$  might still be affected seriously in hostile environments [5]. Besides, the power supply voltage is likely to be an unreliable source, particularly in those hand-held TV sets. However, several clamping voltages are needed to extract the clock information in the received NTSC signal such that the peak white, black level, clip level, and sync tips can be correctly extracted and separated. The architecture of the proposed sync separator is shown in Fig. 1. The bias voltages generated by the High-PSR Bias are fed to OSC as well as Sync Generator. OSC is in charge of generating a stable clock, which is set to 12.0 MHz in this work, to the following DSP core. On the other hand, the digital to analog converter (DAC) converts digital signals from the DSP core into a voltage which is monitored by auto-gain control (AGC) to dynamically adjust threshold voltages required in the Clamper block.

# 2.1 High PSR bias generator

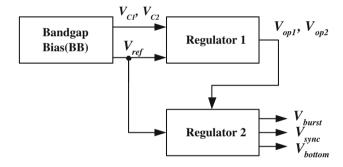

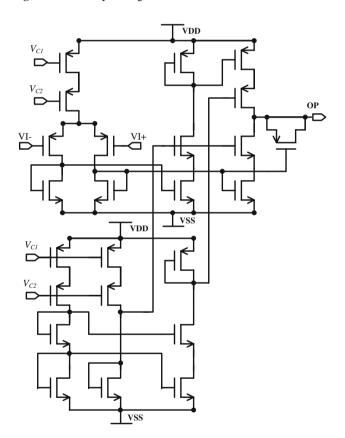

The performance of the entire NSS highly depends upon the sensitivity of the bias, i.e., High-PSR Bias in Fig. 1. The proposed bias circuit comprising two cascaded regulators, and a bandgap bias (BB) with high PSR, is proposed to resolve the difficulty of generating the required clamping voltages.

Fig. 1 Architecture of the proposed NTSC sync separator

The temperature independent bias generated by the BB, called  $V_{ref}$ , is fed into the plus input of the OP-AMP in Regulator 1 as well as the minus input of the OP-AMP in Regulator 2. Meanwhile, the BB also supplies a pair of bias voltages,  $V_{C1}$ ,  $V_{C2}$ , to control the gate drives of the cascode pair in Regulator 1 which in turn stabilizes the source current (tail current) of the built-in OP-AMP ( $A_{OP2}$ ) in Regulator 1, as shown in Fig. 2 and Fig. 4.

# 2.2 High PSR bandgap

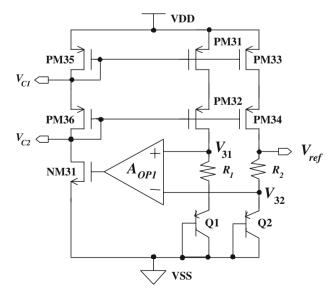

The bandgap reference, i.e., BB, is shown in Fig. 3. Notably, the cascode configuration comprising PM31, PM32, PM33, PM34, PM35, and PM36, and the feedback loop consisting of OP-AMP  $A_{OP1}$  and NM31 are employed to resist the noise coupled with the power supply, VDD. The output impedance from  $V_{ref}$  looking into the drain of PM34 will be increased to around  $g_m r_o^2$  at the sacrifice of the "headroom" of the output swing. However, since the the circuitry is aimed at the clamping voltage generation

Fig. 2 The proposed high-PSR bias circuit

Fig. 3 The bandgap reference

which is usually below 2.0 V, it will not cause any problem. Meanwhile,  $A_{OP1}$  monitors the voltage difference between node  $V_{31}$  and  $V_{32}$  to control the current via NM31, which in turn stabilizes the voltage of the PMOS cascode configuration,  $V_{C1}$  and  $V_{C2}$ .

Assume  $A_1$  and  $A_2$  are the area of the BJTs,  $Q_1$  and  $Q_2$ , respectively. The expected  $V_{ref}$  is analyzed as follows.

$$V_{ref} = I_2 \times R_2 + V_{EB2} = V_{EB2} + L \times V_T \times \ln(K),$$

(1)

where K is the BJT area ratio, i.e.,  $A_1/A_2$ , the ratio of  $R_2/R_1$  is assumed to be L. Hence, the bandgap reference can be pre-determined by tuning L and K.

# 2.2.1 PSR analysis

Since the NM31 acts as a current subtractor to control the gate drives of PM32, PM34, and PM36, we simply analyze the voltages applied to the plus and minus inputs of the OP-AMP  $A_{OP1}$  to find out the PSR which is defined as:  $V_{32} = \frac{1}{R_2 + \frac{1}{g_{mQ2}} + g_{mp} r_{op}^2} \times VDD$ ,  $V_{31} = \frac{R_1 + \frac{1}{g_{mQ1}}}{R_1 + \frac{1}{g_{mQ1}} + g_{mp} r_{op}^2} \times VDD$ , where  $g_{mQ_1}$  and  $g_{mQ_2}$  denotes the transconductance of  $Q_1$  and  $Q_2$ , respectively,  $g_{mp}$  and  $r_{op}$  represents the transconductance and the output impedance of the PMOS transistors in the cascode configuration. Thus, the PSR is found to be,

$$PSR \approx \frac{VDD}{V_{32} - V_{31}} \times \frac{1}{A_{OP1}} \approx \frac{1}{\frac{R1}{g_{mp}r_{op}^2}} \times \frac{1}{A_{OP1}}$$

(2)

The  $A_{OP1}$  is supposed to be an ideally large gain to avoid other side effects. Hence, we can reduce  $\frac{R_1}{g_{mp}r_{op}^2}$  to increase the PSR by a small  $R_1$  and a cascode configuration.

#### 2.2.2 Cascaded regulators

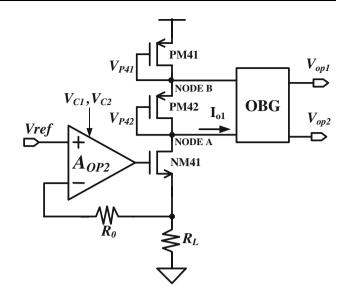

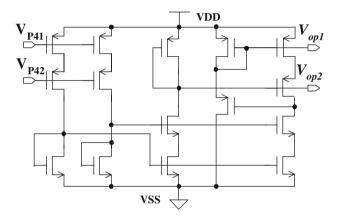

One of the most efficient approaches to avoid the effects of unstable power supplies is to employ step-down bandgap-referenced voltage regulators to supply a temperature independent reference voltage,  $V_{ref}$ , to the rest of the circuitry [10]. Since the received  $V_{pp}$  might be as low as 2.0 V, the generated  $V_{ref}$  should be no higher than this lower bound. Referring to Fig. 4, Regulator 1 is composed of PM41, PM42, NM41,  $R_0$ ,  $R_L$ , and OP-AMP  $A_{OP2}$ .  $A_{OP2}$  is shown in Fig. 5, where the  $V_{C1}$  and  $V_{C2}$  are supplied by the bandgap reference.

Notably, PM41 and PM42 are cascoded to provide a high output impedance and two stable reference voltages,  $V_{P41}$ ,  $V_{P42}$  to the following OPA Bias Generator (OBG). With large  $\frac{\partial I_{o1}}{\partial V_{o1}}$  ( $V_{o1}$  is the voltage at NODE A.), the loading effect at NODE A can be reduced. Assume  $R_{out1}$  is the output impedance from OBG looking into NODE A.

Fig. 4 The circuitry of Regulator 1

Fig. 5 The circuitry of  $A_{OP2}$

$g_{m_PM41}$  and  $g_{m_PM41}$  are the transconductances of PM41 and NM41, respectively. Since PM41 and PM42 are sized equally, the transconductance of PM42 is equal to  $g_{m_{PM41}}$ . The relationship between  $\frac{\partial I_{o1}}{\partial V_{o1}}$  and  $R_{out1}$  can be derived as:  $\frac{\partial I_{o1}}{\partial V_{o1}} = \frac{1}{R_{out1}}$ . NM41 has become a Common Source amplifier with source degeneration in the small-signal AC model. Besides, the output impedance of  $A_{OP2}$ ,  $r_{OA2}$ , is relatively

small compared to the gate impedance of NM41. We then can easily derive the impedance looking A node from OBG as  $R_{out1} \approx \frac{2}{g_{m_{PM41}}} \parallel (1 + g_{m_{NM41}}(R_o \parallel R_L)) \cdot r_{o_{NM41}} \approx \frac{2}{g_{m_{PM41}}} \parallel (g_{m_{NM41}} \cdot r_{o_{NM41}} \cdot (R_o \parallel R_L)) \approx \frac{2}{g_{m_{PM41}}}$ , where  $r_{o_{NM41}}$  is the output impedance of NM41.

Because of small  $R_{out1}$ ,  $\frac{\partial I_{o1}}{\partial V_{o1}}$  will be large enough to ignore the loading effect such that stable bias voltages can be achieved. Similar results can be derived at NODE B.

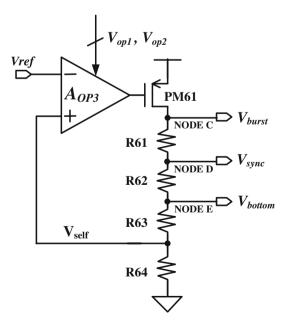

Figure 6 shows the schematic of OBG. The regulated voltages,  $V_{P41}$  and  $V_{P42}$ , are translated to another pair of voltage levels,  $V_{op1}$  and  $V_{op2}$ . The output bias of OBG,  $V_{op1}$  and  $V_{op2}$ , are used to control the tail current of the differential stage of  $A_{OP3}$ . Regulator 2 comprising  $A_{OP3}$ , PM61, and a resistor string, is shown in Fig. 7. Notably,  $A_{OP3}$  is identical to  $A_{OP2}$  except that the bias voltages,  $V_{C1}$  and  $V_{C2}$ , in  $A_{OP2}$  are replaced with  $V_{op1}$  and  $V_{op2}$ , respectively.

Fig. 6 The schematic of OBG

Fig. 7 The circuitry of Regulator 2

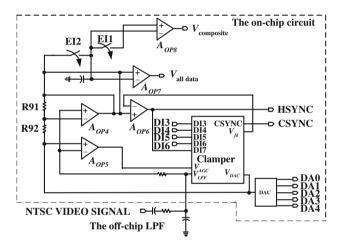

### 2.3 Clamper and timing

The generated  $V_{burst}$ ,  $V_{sync}$ , and  $V_{bottom}$ , are fed into the Clamper shown in Fig. 8 to serve as the slicing thresholds. The NTSC signal will be coupled to the clamper via a LPF (low pass filter) with a 600 KHz stopband. By contrast, if the color burst signal is also taken into account, the LPF can be switched to a 3.58 MHz stopband. The external digital control signals, DI3, ..., DI6, cooperated with the output of  $A_{OP6}$ , i.e., DI7, to control the switches in the clamper, as shown in Fig. 8. The truth table of the digital control block is given in Table 1.

The output voltage of the digital-to-analog converter (DAC) is coupled to the positive input of  $A_{OP5}$  where the negative input is the  $V_{LPF}$ , which is the output of the filtered NTSC signal. The output of  $A_{OP5}$  is fed into the gate drive of NM101 in Fig. 9 which is the schematic of the

Fig. 8 Architecture of the clamper, sync generator, and the DAC

Table 1 Truth table of the digital control block

| Input  |      |      |      |         |     |     |

|--------|------|------|------|---------|-----|-----|

| DI3    | DI4  | DI5  | DI6  | DI7     |     |     |

| 0      | 0    | X    | X    | X       |     |     |

| 0      | 1    | X    | X    | X       |     |     |

| 1      | 0    | X    | X    | X       |     |     |

| 1      | 1    | 1    | 0    | 1       |     |     |

| Output |      |      |      |         |     |     |

| SW00   | SW01 | SW02 | SW03 | Clamper | DO1 | DO2 |

| ON     | OFF  | ON   | OFF  | ON      | 0   | 1   |

| ON     | OFF  | ON   | OFF  | ON      | 0   | 1   |

| OFF    | X    | OFF  | ON   | OFF     | 1   | 0   |

| ON     | OFF  | OFF  | OFF  | ON      | 0   | 1   |

Fig. 9 Schematic of the clamper

Clamper. Namely, it is the auto gain control (AGC) pin to dynamically adjust the threshold voltage level. In short, the operation of the AGC loop comprising Clamper and  $A_{OP5}$  is summarized as follows.

$$V_{LPF}\uparrow \Rightarrow V_{AGC}\downarrow \Rightarrow$$

$V_DAC = V_LPF$ , when SW00 is turned on  $\Rightarrow V_LPF$  stable.

Thus, the DAC output voltage serves as a dynamically adjustable level to determine and clamp the NTSC video signal.

# 2.4 Sync generator

The proposed sync separator also generates two critical digital signals which will be utilized in any following DSP core.

*HSYNC*: HSYNC is generated at the output of  $A_{OP6}$  by comparing the  $V_{fd}$  which is a DC level provided by Clamper and the output of  $A_{OP4}$  which is a threshold voltage level.

$V_{all\ data}$ : This signal is present at the output of  $A_{OP7}$  which comprises all of the edges of the original NTSC

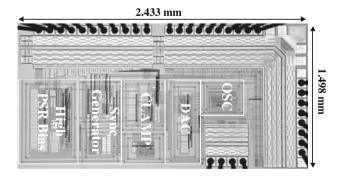

Fig. 10 Diephoto of the proposed sync separator

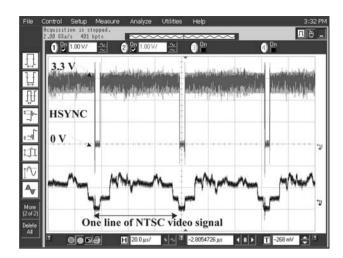

$\begin{tabular}{ll} Fig. 11 & The measured HSYNC and the corresponding input NTSC signal \\ \end{tabular}$

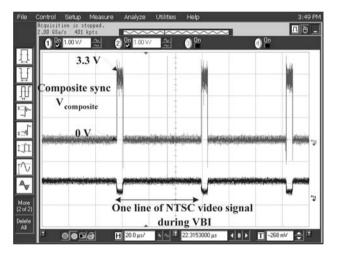

Fig. 12 The measured  $V_{composite}$  and the corresponding input NTSC signal

Fig. 13 The measured  $V_{alldata}$  and the 0 input NTSC signal

Table 2 Specifications

comparison with prior works

|                               | Ours                                                         | [5]                                                          | [8]                                    | [7]                        |

|-------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------|----------------------------|

| Process                       | 0.35 μm CMOS                                                 | N/A                                                          | N/A                                    | 0.5 μm CMOS                |

| Generated signals             | H-sync,<br>V-sync,<br>C-sync,<br>12 MHz CLK,<br>Line-21 data | Burst<br>output,<br>V-sync,<br>C-sync,<br>Odd/even<br>output | H-sync,<br>V-sync,<br>C-sync,<br>Phase | comparator<br>output       |

| H-sync                        |                                                              |                                                              |                                        |                            |

| V-sync,                       |                                                              |                                                              |                                        |                            |

| C-sync                        |                                                              |                                                              |                                        |                            |

| Temp. (°C)                    | 0–70                                                         | 0-70                                                         | -20 - 75                               | N/A                        |

| Power (mW)                    | 31.92                                                        | 1100                                                         | 350                                    | N/A                        |

| Supply voltage (V)            | 3.3                                                          | 5                                                            | 5                                      | 3.3                        |

| Year                          | 2006                                                         | 2003                                                         | N/A                                    | 1998                       |

| Performance with supply noise | Functional worked with 1 V supply noise                      | N/A                                                          | N/A                                    | 28 dB power supply immuity |

signal. When EI2 is turned on, the clamped NTSC signals are sampled. On the other hand, the clamped NTSC signals are hold when EI2 is turned off. Thus, the comparing reference voltage level needed on the negative input of  $A_{OP7}$  is obtained by means of the hold operation.

$V_{composite}$ : By the combination of switches EI1 and EI2,  $A_{OP8}$  outputs a waveform composed of VSYNC and HSYNC which are both required in the later DSP operations. Because of the different line delay caused by EI1 and EI2, the clamped NTSC signal has the cross voltage drops on the sync tip between positive and negative inputs of  $A_{OP8}$ . Consequently, the composite sync signal could be generated by voltage comparison.

# 3 Implementation and measurement

Taiwan Semiconductor Manufacturing Company (TSMC)  $0.35 \mu m$  2P4M CMOS process was adopted to carry out the proposed design. According to Eq. 1, the following equality for a temperature-independent bandgap reference is derived.

$$\frac{\partial V_{ref}}{\partial T} = L \times \ln(K) \times \frac{\partial V_T}{\partial T} + \frac{V_{EB2}}{\partial T} = 0$$

(3)

By substituting all of the parameters in the above equation and setting L=10, K=8,  $R_1=140~\Omega$ , the  $V_{ref}$  is found to be approximately 1.15 V. Then, we select the most common clamping voltages for the NTSC signal given a 3.3 V power supply:  $V_{burst}=3.05~\rm V$ ,  $V_{sync}=1.78~\rm V$ , and  $V_{bottom}=1.57~\rm V$ , to design the entire bias circuitry. The simulation and measurement results show that the proposed BGC, which does not require any compensation capacitor, possesses 34 and 30 dB PSR up to 1 MHz,

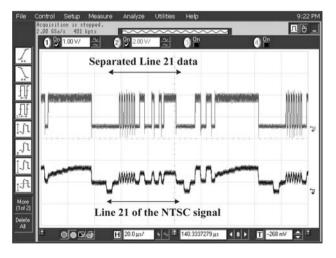

Figure 11 shows the separated HSYNC signal and the corresponding input NTSC signal measured on silicon when a noise with a magnitude of 1 V is present in the power supplies. Figure 12 reveals the signal  $V_{composite}$ , which is the composite sync signal. The NTSC signal shown in Fig. 12 is the vertical blanking interval (VBI) of the NTSC video signal. The separated Line 21 data is shown in Fig. 13. he power consumption of the proposed design is measured to be 31.92 mW. Table 2 lists the specifications of the proposed design compared with several prior works.

# 4 Conclusion

We have proposed a temperature-insensitive high-PSR bias generation circuitry for the sync separation of NTSC signals in this paper. The cascode configuration as well as the cascaded regulators stabilize the clamping levels to cope with hostile receiving environments. Besides the physical implementation, the detailed PSR analysis of the proposed design is also revealed to illustrate our methodology. According to the measurement results, all of the required sync signals are successfully extracted for any later digital signal processing even if a large noise is coupled in the supply voltage.

Acknowledgements This research was partially supported by National Science Council under Grant NSC94-2213-E-110-024 and

NSC94-2213-E-110-022. Furthermore, the authors would like to express their deepest gratefulness to Chip Implementation Center (CIC) of National Applied Research Laboratories (NAPL), Taiwan, for their thoughtful chip fabrication service. The authors also like to thank "Aim for Top University Plan" project of NSYSU and Ministry of Education, Taiwan, for partially supporting the research.

#### References

- Buck, A. E., McDonald, C. L., Lewis, S. H., & Viswanathan, T. R. (2002, January). A CMOS bandgap 0 without resistors. *IEEE Journal of Solid-State Circuits*, 37(1), 81–83.

- Giustolisi, G. & Palumbo, G. (2001, May). Detailed frequency analysis of power supply rejection in Brokaw bandgap. *The 2001 IEEE international symposium on circuits and systems* (Vol. 1, pp. 731–734).

- Jack, K. (2001). Video demystified. Reading: published by LLH Technology Publishing.

- Jun, C., & Guican, C. (2001, October). A CMOS bandgap reference circuit. 2001 4th International Conference on ASIC (pp. 271–273).

- National Semiconductor. (2003, June). LM1881 video sync separator. Data Sheet

- Ohta M., Kohiyama, K., Tahara, N., Sugihara, K., Asami, F., Kobayashi, O., Hino, Y., & Akiba, T. (1990, December). A single-chip CMOS analog/digital mixed NTSC decoder. *IEEE Journal of Solid-State Circuits*, 25(6), 1464–1469.

- Redman-White, W., Duffee, R., Bramwell, S., Rijns, H., James, S., Tijou, J., & van der Weide, G. (1998). A robust analog interface system for submicron CMOS video DSP. *IEEE Journal Solid-State Circuits*, 33(7), 1076–1081.

- ROHM CO., LTD, SYNC separator IC with AFC. Data Sheet: BA7071F.

- Routama, J., Koli, K. & Halonen, K. (1998, May). A novel ringoscillator with a very small process and temperature variation. 1998 International symposium on circuits and systems (ISCAS'98) (Vol. 1, pp. 181–184).

- Sundaresan, K., Brouse, K. C., U-Yen, K., Ayazi, F., & Allen, P. E. (2003, May). A 7-MHz process, temperature and supply compensated clock oscillator in 0.25 μm CMOS. 2003 International symposium on circuits and systems (ISCAS'03) (Vol. 1, pp. 693–696).

- Techwell, Inc. (2000, March 30). Enhanced NTSC/PAL/SECAM Video Decoder, Data Sheet: TW99.

Chua-Chin Wang was born in Taiwan in 1962. He received the B.S. degree in Electrical Engineering from National Taiwan University in 1984, and the M.S. and Ph.D. degree in Electrical Engineering from State University of New York in Stony Brook in 1988 and 1992, respectively. He then joined the Department of Electrical Engineering, National Sun Yat-Sen University, Taiwan, and became a full professor since 1998. His recent research interests include

mixed-signal circuit design, low-power and high-speed circuit design, communication interfacing circuitry, and bio-chips. He founded SOC group in Department of Electrical Engineering, National Sun Yat-Sen

University during 2005. He is currently also serving as the Director of Engineering Technology Research and Promotion Center (ETRPC), National Sun Yat-Sen University. He is the Chair of IEEE Circuits and Systems Society (CASS), Tainan Chapter. He is also the founding Chair of IEEE Solid-State Circuits Society (SSCS), Tainan Chapter, and the founding Councilor of IEEE NSYSU Student Branch. He is also a member of the IEEE CASS Multimedia Systems Applications (MSA), VLSI Systems and Applications (VSA), Nanoelectronics and Giga-scale Systems (NG), and Biomedical Circuits and Systems (BioCAS) Technical Committees. He is a senior member of IEEE since 2004. Currently he is also serving as the Associate Editor of International Journal of VLSI Design, and IEICE Trans, on Electronics. He is also a Guest Editor of International Journal of Electrical Engineering. In 2007, he was elected to be IEEE CASS Nanoelectronics and Giga-scale Systems (NG) Technical Committee Chair to serve a 2-year term from 2008. In the same year, he was elected to be the DLP (Distinguished Lecturer Program) speaker of IEEE Circuits and Systems Society. He was the General Chair of 2007 VLSI/CAD Symposium.

Chia-Hao Hsu was born in Taiwan in 1981. He received the B.S. and M.S. degree in Department of Electronic Engineering in Southern Taiwan University in 2005 and 2007, respectively. He is currently working toward the Ph.D. in the Department of Electrical Engineering, National Sun Yat-Sen University, Kaohsiung, Taiwan. His recent research interests include VLSI design and mixed-signal integrated circuit design.

Chi-Chun Huang was born in Taiwan in 1980. He received his B.S. degree in Department of Electrical Engineering National Cheng Kung University in 2003 and the M.S. in Department of Electrical Engineering in National Sun Yat-Sen University in 2005. He is currently working toward the Ph.D. in Department of Electrical Engineering National Sun Yat-Sen University, Kaohsiung, Taiwan. His recent research interests include VLSI design,

mixed signal circuits, and biomedical signal processing.

Tzung-Je Lee was born in Taiwan in 1979. He received the B.S., M.S., and Ph.D. degrees in Electrical Engineering from National Sun Yat-Sen University, Taiwan, in 2002, 2004, and 2008, respectively. His current research interests are VLSI design, mixed-signal circuit design, and implantable biochips.

Chien-Chih Hung received the B.S. and M.S. degrees in Electrical Engineering from National Sun Yat-Sen University, Taiwan, in 2003 and 2005, respectively. His current research interests are VLSI design, mixed-signal circuit design, and communication circuits.

and bio-chips.

Ya-Hsin Hsueh was born in Taiwan in 1976. She received the B.S., M.S. and Ph.D degree in Electrical Engineering from National Sun Yat-Sen University in 1998, 2000, and 2004, respectively. She then joined the Department of Electronic Engineering, National Yunlin University of Science and Technology, Taiwan, as an assistant professor since 2005. Her recent research interests include mixed-signal circuit design, digital circuit design, FPGA system,

Ron Hu was born in Tainan, Taiwan, in 1962. He received the B.S. degree from National Taiwan Institute of Technologies, Taipei, Taiwan, in 1987, the M.S. degree from Utah State University, Logan, in 1990, and the Ph.D. degree from the State University of New York, Stone Brook, 1994, all in electrical engineering. He jointed Holtek Semiconductor Inc., Taiwan, in 1994. He became General Manager of Asuka Semicon-

ductor, Inc., Hsin-Chu, Taiwan, in 2001. His research interests include consumer product circuit design and wireless communication.